# RC224ATF Integrated V.22 bis Data/Fax Modem with "AT" and Class 1 Commands Rockwell (Group 3 Transmit and Receive Functions)

### INTRODUCTION

The Rockwell RC224ATF is a combination V.22 bis data and Group 3 facsimile (fax) CMOS modem in a single VLSI package. The RC224ATF integrated data/fax modem is available in either a 68-pin plastic leaded chip carrier (PLCC) or a 100-pin plastic guad flat pack (PQFP).

The RC224ATL is identical to the RC224ATF except that fax modes are not included. In this document, all references to the RC224ATF apply to the RC224ATL except for fax modes and where otherwise stated.

Optimized for battery-powered portable designs, the RC224ATF modern provides maximum integration and functionality through a low power, small footprint, minimum supporting component design resulting in a highly compact, low cost, universal data/fax application solution.

Data modes, controlled by an industry standard 2400 "AT" command set, can transmit and receive up to 2400 bps.

Fax modes, controlled by a built-in EIA-578 Class 1 command interface, provide Group 3 transmit and receive

Full error correction (V.42 LAPM, MNP2-4) and data compression (V.42 bis, MNP 5) capabilities are supported in both the RC224ATF and the RC224ATL through the Rockwell Protocol Interface (RPI™) and host communication software supporting the RPI. A list of communication software supporting the RPI can be obtained from your local Rockwell sales representative.

The modem has a selectable parallel or serial interface to the host (DTE). When parallel mode is selected, a 16C450-compatible interface allows direct connection to a notebook, laptop, or PC-compatible bus without an external UART. When serial mode is selected, a CCITT V.24 logic-compatible interface with TTL levels is supplied along with indicator outputs.

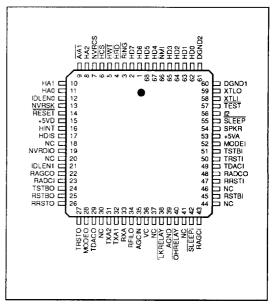

The RC224ATF packaged in a 68-pin PLCC is shown in Figure 1.

The RC224ATF Designer's Guide (Order No. 821) provides detailed interface, AT command, and S register information.

BPI is a trademark of Bockwell International

#### **FEATURES**

- Data modes

- CCITT V.22 bis (2400 bps), V.22 (1200 bps)

- Bell 212A (1200 bps) and 103 (300 bps)

- Enhanced AT commands

- Group 3 fax modes

- V.29 (9600/7200 bps) transmit

- V.27 ter (4800/2400 bps) transmit and receive

- V.21 Channel 2 (300 bps) transmit and receive

- EIA-578 Service Class 1 commands

- V.42/MNP2-4 and V.42 bis/MNP 5 support (through RPI™ and host software) without additional hardware

- Data/fax discriminator and auto answering

- Communications software compatible

- Integrated call progress and dialing

- No external microcomputer or memory required

- Parallel or serial asynchronous DTE interface

- Built-in hybrid allows direct connect to telco transformer

- A/A1 relay control

- NVRAM interface allows storage of two user configurations and four 36-digit dial strings

- Automatic adaptive/ fixed compromise equalization

- Programmable sleep mode and wake-up

- Full-duplex data mode test capabilities: Analog loop, local digital loop, and remote digital loop

- Half-duplex fax mode test capabilities

- Single voltage operation: +5 VDC ± 5%

- Low power CMOS

- Operating: 150 mW (typical)

- Sleep Idle: 30 mW (typical)

- Sleep Stop: 2 mW (typical)

- Package options:

- 68-pin plastic leaded chip carrier (PLCC)

- 100-pin plastic quad flat pack (PQFP)

### **TECHNICAL SPECIFICATIONS**

#### General

The RC224ATF modem is a full-featured, self-contained data/fax solution. No external microcontroller for data or fax control functions is required. Dialing, call progress, and telephone line interface functions are fully supported and controlled through the AT command set.

Data modes perform complete handshake and data rate negotiations. All tone and pattern detection required by the applicable CCITT or Bell standard are supported.

Fax modes support Group 3 fax requirements. Fax data and fax control (V.21 300 bps) performed by the modem is controlled and monitored through the fax EIA-578 Class 1 command interface. Full HDLC formatting, flag insertion/deletion, and CRC generation/checking is provided.

Figure 1. RC224ATF Modem in a 68-Pin PLCC

Both transmit and receive fax data is buffered within the modem. Data transfer to and from the DTE is flow controlled by XON/XOFF.

### Configurations and Rates

The supported modem configurations and signalling rates are listed in Table 1. In data modes with serial interface selected, DTE rate offsets of +1%, -2.5% are accommodated by adding/deleting stop bits as required. In fax modes, the DTE rate is 19200 bps.

#### Operation

Modem operation is controlled by AT commands (Table 2), fax service class 1 commands (Table 3), and supporting S registers (Table 4). Result codes and messages are listed in Table 5.

**Data Modes:** Data rate selection is determined by the speed of the originating and answering modems:

| Originate Modem |      | ect Speed Ba<br>er Modem Ra |      |

|-----------------|------|-----------------------------|------|

| Rate (bps)      | 300  | 1200                        | 2400 |

| 300             | 300  | 300                         | 300  |

| 1200            | 1200 | 1200                        | 1200 |

| 2400            | 1200 | 1200                        | 2400 |

Fax modes: Fax modes are negotiated as defined in T.30 and are implemented by AT+F commands. The AT+FCLASS=1 command causes entry into the fax mode from the data mode. Most other fax class 1 commands, which start with the AT+F prefix, are valid only in the fax mode. All data commands are valid in the fax mode except A/, On, &Tn, and the escape sequence (+++). The AT+FCLASS=0 command terminates the fax mode and causes entry into the data mode.

| Table 1. | Configurat | lons | and | Rates |

|----------|------------|------|-----|-------|

|----------|------------|------|-----|-------|

| Configuration | Modulation         |                                                | ter Carrier<br>(Hz) ±0.01% | Data Rate<br>(bps)                      | Baud<br>(Symbols/Sec.)                              | Bits Per<br>Symbol | Constellation<br>Points |

|---------------|--------------------|------------------------------------------------|----------------------------|-----------------------------------------|-----------------------------------------------------|--------------------|-------------------------|

| Data Mode     |                    | Answer                                         | Originate                  | • • • • • • • • • • • • • • • • • • • • |                                                     |                    |                         |

| V.22 bis      | QAM                | 2400                                           | 1200                       | 2400                                    | 600                                                 | 4                  | 16                      |

| V.22          | DPSK               | 2400                                           | 1200                       | 1200                                    | 600                                                 | 2                  | 4                       |

| Bell 212A     | DPSK               | 2400                                           | 1200                       | 1200                                    | 600                                                 | 2                  | 4                       |

| Bell 103      | FSK                | 2225 M<br>2025 S                               | 1270 M<br>1070 S           | 300                                     | 300                                                 | 1                  | 1                       |

| Fax Mode      |                    | Receive                                        | Transmit                   |                                         |                                                     |                    | ·                       |

| V.29          | QAM<br>QAM         | NA<br>NA                                       | 1700<br>1700               | 9600<br>7200                            | 2400<br>2400                                        | 4<br>3             | 16<br>8                 |

| V.27 ter      | DPSK<br>DPSK       | 1800<br>1800                                   | 1800<br>1800               | 4800<br>2400                            | 1600<br>1200                                        | 3<br>2             | 8<br>4                  |

| V.21          | FSK                | 1650 M<br>1850 S                               | 1650 M<br>1850 S           | 300                                     | 300                                                 | 1                  | 1                       |

| D             | PSK = Differential | Amplitude Mo<br>Phase Shift Ke<br>Shift Keying |                            | M =<br>S =<br>NA =                      | Mark condition<br>Space condition<br>Not applicable | ****               |                         |

Table 2. "AT" Command Set Summary

| Basic Comma        | nd Function                                                         |

|--------------------|---------------------------------------------------------------------|

| AT                 | Attention Code                                                      |

| Α                  | Answer Command                                                      |

| <u>A</u>           | Repeat Last Command                                                 |

| Bn                 | Communications Standard Option                                      |

| C1                 | Carrier Control Option                                              |

| D                  | Dial Command                                                        |

| En<br>F1           | Off-line Character Echo Option                                      |

| FI<br>Hn           | On-line Character Echo Option<br>Switch Hook Control Option         |

| In                 | Identification/Checksum Option                                      |

| Ln                 | Speaker Volume Option                                               |

| Mn                 | Speaker Control Option                                              |

| On                 | On-line Command                                                     |

| P                  | Pulse Dial                                                          |

| Qn                 | Result Code Display Option                                          |

| Sn                 | Select an S Register                                                |

| Sn=                | Write to an S Register                                              |

| Sn?                | Read an S Register                                                  |

| T                  | Touch Tone Dial                                                     |

| Vn                 | Result Code Form Option                                             |

| Xn                 | Result Code Set/Call Progress Option                                |

| Yn                 | Long Space Disconnect Option                                        |

| Zn                 | Recall Stored Profile Command                                       |

| +++                | Escape Code Sequence                                                |

| ?<br>Dial Modifier | Returns Last Addressed S Register Function                          |

|                    |                                                                     |

| P                  | Pulse Dial                                                          |

| R                  | Originate Call in Answer Mode                                       |

| S=n                | Dial Stored Number (n=0:3)*                                         |

| T<br>W             | Touch Tone Dial<br>Wait for Dial Tone                               |

|                    | Return to Idle State                                                |

| ,<br>@             | Wait for Quiet Answer Command                                       |

| l G                | Flash Hook                                                          |

| •                  | Pause                                                               |

| ,<br>0–9, A, B,    | Dial Digits/Characters                                              |

| C,D, #, *          |                                                                     |

| & Command          | Function                                                            |

| &Cn                | Data Carrier Detect Option                                          |

| &Dn                | Data Terminal Ready Option                                          |

| &F                 | Load Factory Defaults                                               |

| &Gп                | Guard Tone Option                                                   |

| &Jn                | Auxiliary Relay Control                                             |

| &LO                | Dial up Line                                                        |

| &MO                | Asynchronous Communications Mode                                    |

| &Pn                | Make to Break Ratio Selection                                       |

| &Q0                | Asynchronous Communications Mode                                    |

| &Sn                | Data Set Ready Option                                               |

| &Tn                | Test Command Selection                                              |

| &V<br>&Wn          | View Active Configuration and User Profiles<br>Store Active Profile |

| &X0                | Asynchronous Data Transmission                                      |

| &Yn                | Select Stored Profile on Powerup Option                             |

| &Zn=x              | Store Telephone Number (n=0:3)                                      |

| % Command          |                                                                     |

| %Dn                | DTMF Level Attenuation                                              |

| %Ln                | Transmit Level Attenuation                                          |

| %J                 | Load Secondary Defaults                                             |

|                    |                                                                     |

Table 3. Fax Command Set Summary

| Fax Command                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +FCLASS=n<br>+F <command/> ?<br>+F <command/> =?<br>+FAA=n<br>+FF<br>+FTS=n<br>+FTS=n<br>+FTM=n<br>+FTM=n<br>+FTH=n<br>+FTH=n<br>+FTH=n<br>+FRH=n<br>+FRTn<br>+FTTn=m | Select Service Class Report Active Configuration Report Operating Capabilities Data/Fax Auto Answer Enhanced Flow Control Stop Transmission and Wait Receive Silence Transmit Data Receive Data Transmit Data with HDLC Framing Receive Data with HDLC Framing Receive Test Data Transmit Test Data Rockwell Protocol Interface (RPI) Enable |

Table 4. S Register Summary

| Register        | Function                                            |  |  |

|-----------------|-----------------------------------------------------|--|--|

| S0*             | Ring to Answer On                                   |  |  |

| S1              | Ring Count                                          |  |  |

| S2              | Escape Code Character                               |  |  |

| S3              | Carriage Return Character                           |  |  |

| S4              | Line Feed Character                                 |  |  |

| S5              | Back Space Character                                |  |  |

| S6              | Wait for Dial Tone                                  |  |  |

| <b>S</b> 7      | Wait Time for Data Carrier                          |  |  |

| S8              | Pause Time for Comma                                |  |  |

| S9              | Carrier Detect Response Time                        |  |  |

| S10             | Lost Carrier to Hang-up Delay                       |  |  |

| S11             | DTMF Dialing Speed                                  |  |  |

| S12             | Escape Code Guard Time                              |  |  |

| S14*            | Bit Mapped Options Register                         |  |  |

| S16             | Modem Test Options                                  |  |  |

| S17             | Fax Mode Null Byte Timer                            |  |  |

| S18*            | Test Timer                                          |  |  |

| S19             | Rockwell Protocol Interface (RPI) Speed             |  |  |

| S20             | Fax Mode Inactivity Timer                           |  |  |

| S21*            | Bit Mapped Options Register                         |  |  |

| S22*            | Bit Mapped Options Register                         |  |  |

| S23*            | Bit Mapped Options Register                         |  |  |

| S24             | Sleep Mode Inactivity Timer                         |  |  |

| S25*            | Delay to DTR                                        |  |  |

| S26*            | RTS to CTS Delay Interval                           |  |  |

| S27*            | Bit Mapped Options Register                         |  |  |

| S28*            | Bit Mapped Options Register                         |  |  |

| * This S-Regist | * This S-Register is stored in the modem NVRAM upon |  |  |

This S-Register is stored in the modem NVRAM upon receipt of the &W command so that the contents are preserved when modem power is removed.

Table 5. Result Codes and Messages

| Digit<br>Code | Word Code    | Meaning                                                                                  |  |

|---------------|--------------|------------------------------------------------------------------------------------------|--|

| 0             | ок           | Command line executed without errors.                                                    |  |

| 1             | CONNECT      | Connection at 300 bps.                                                                   |  |

| 2             | RING         | Ringing signal detected.                                                                 |  |

| 3             | NO CARRIER   | Carrier lost or never present.                                                           |  |

| 4             | ERROR        | Invalid command, checksum, error in command line, or command line exceeds 40 characters. |  |

| 5             | CONNECT 1200 | Connection at 1200 bps                                                                   |  |

| 6             | NO DIALTONE  | No dial tone detected.                                                                   |  |

| 7             | BUSY         | Busy signal detected.                                                                    |  |

| 8             | NO ANSWER    | No silence detected when dialing a system not providing a dial tone.                     |  |

| 10            | CONNECT 2400 | Connection at 2400 bps.                                                                  |  |

| +F4           | +FCERROR     | Fax carrier error.                                                                       |  |

| 13            | DATA         | Connected as data modem during auto answer.                                              |  |

| 15            | FAX          | Connected as fax modem during auto answer.                                               |  |

### Data/Fax Auto Answering

The modem can automatically determine if the incoming call is from a data or fax modem, make the appropriate connection, and inform the DTE of the connection type.

### **AT Command Format**

Each command line must start with the AT prefix and be terminated with a carriage return (CR). Several commands may be included on one command line. A command line may contain up to 40 characters excluding the AT prefix and the terminating CR. A separator is not required between data commands. A semicolon (;) separator is required between fax commands.

AT commands are composed of 10-bit ASCII encoded asynchronous characters. The character format in data mode is 8 data bits with no parity, or 7 data bits with even, odd, or no (two stop bits) parity, at a data rate of 19200, 2400, 1200, or 300 bps. The character format in fax mode is 8 data bits with no parity at 19200 bps.

#### **Data Modulation**

The data modulation conforms to V.29, V.27 ter, V.22 bis, V.22, V.21, Bell 212A, or Bell 103, depending on the selected configuration. Transmitter and receiver spectrum shaping is provided in accordance with the applicable standard.

### Equalization

Automatic adaptive equalization as well as fixed compromised equalization is provided to compensate for line distortions and to minimize the effects of intersymbol interference.

### Scrambler/Descrambler

The modem incorporates a self-synchronizing scrambler/descrambler satisfying the applicable CCITT or Bell requirements.

#### Transmit Level

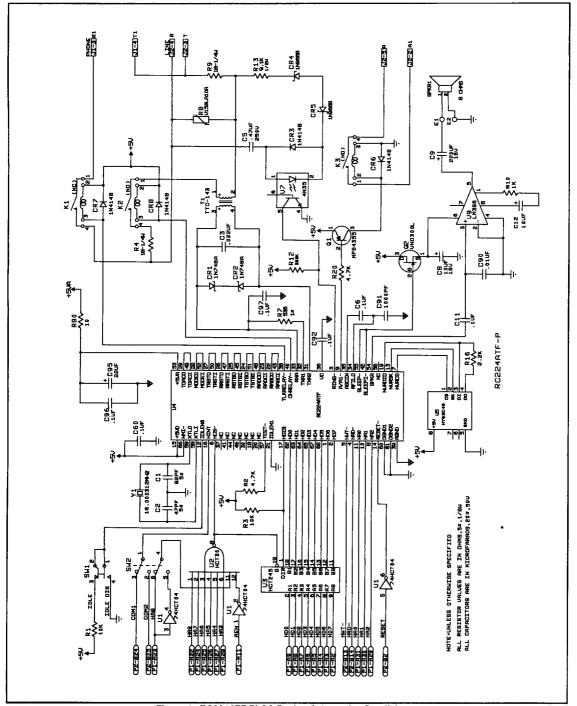

The transmit level is -10 dBm ±1 dB (at TIP and RING) can be obtained using the circuits shown in Figures 4 and 5.

### **Transmit Tones**

Answer Tone: An answer tone of 2100 Hz (V.22 bis, V.22, or T.30) or 2225 Hz (Bell 212A or 103) is generated.

**Guard Tone:** An 1800 Hz guard tone can be generated in all data modes.

Calling Tone: A 1100 Hz (0.5 seconds on, 3 seconds off) calling tone (T.30) is generated in the originate fax mode.

#### Receive Level

The receiver satisfies performance requirements for a received signal from –9 dBm to –43 dBm using the circuit shown in Figure 3. The carrier detect is ON at –43 dBm and OFF at –48 dBm with a minimum of 2 dB hysterisis.

#### Receiver Tracking

The modem can accommodate carrier frequency offset up to  $\pm 7$  Hz, and a transmit timing error of  $\pm 0.01\%$  (V.22 bis or V.27 ter) or  $\pm 0.02\%$  (V.22 or Bell 212A).

### Parallel/Serial Interface Operation

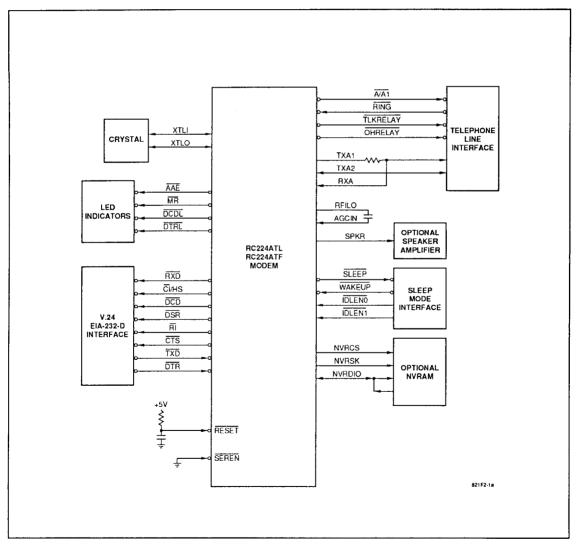

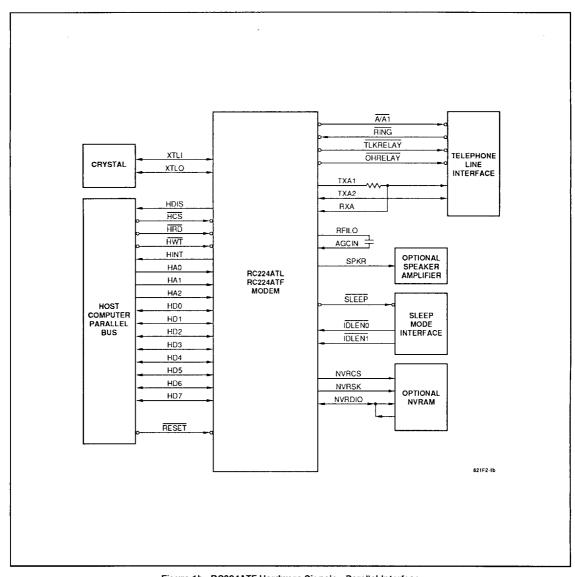

The RC224ATF can be configured to operate with a 16C450-compatible parallel interface or a V.24 (EIA-232-D) logic-compatible serial interface. The functional interface signals are shown in Figure 1.

### Telephone Line Interface

**Telco Interface:** Internal differential drivers allow simple connection to the line transformer, requiring only a single line impedance matching resistor.

Relay control: Complete automatic control of the off-hook, talk/data, and A/A1 relays is provided. Relay drivers allow direct connection to the off-hook and talk/data relays.

DTMF Dialing: Standard DTMF (dual tone multi-frequency) tones (digits 0-9, A, B, C, D, \*, and #) or pulses (digits 0-9) can be generated.

Ring Detection: RING signal is detected from valid high to low transitions on the RING input line at frequencies of 15.3 Hz to 63 Hz. A RING is valid if the RING ON time is greater than 0.125 seconds and is followed by a RING OFF time greater than 0.5 seconds.

#### **NVRAM Interface**

A three-line serial interface to an optional user-supplied 1024-bit non-volatile RAM (NVRAM) is provided. The NVRAM can store up to two user-selectable modem configurations as well as four 36-digit dialing strings.

### Single Device Data/Fax Modem with "AT" Commands

#### Speaker Interface

A SPKR output is provided with on/off and volume control logic incorporated in the modem, requiring only an external amplifier to drive a loudspeaker.

### Low Power Sleep Mode

To conserve power, the RC224ATF has a two selectable sleep (power down) modes - Idle and Stop. If enabled by the IDLEN0 and IDLEN1 inputs, the selected sleep mode is entered whenever the modem is inactive. The sleep mode indicator output, SLEEP, is provided to allow external circuits to be powered down when the modem is in Idle or Stop mode.

The Idle mode allows reduced power consumption with automatic recovery without additional circuitry. If Idle mode is selected, the modem exits Idle mode and returns to full operation whenever a ring signal occurs, the DTE writes to the modem (parallel interface), or WAKEUP input, normally tied to DTR or TXD, is asserted (serial interface).

The Stop mode further reduces power consumption.

### **Power and Environmental Requirements**

The power requirements are specified in Table 6. The environmental specifications are listed in Table 7.

Table 6. Power Requirements

|            | Typical | Typical @ 25°C |         | m @ 0°C |

|------------|---------|----------------|---------|---------|

| Mode       | Current | Power          | Current | Power   |

| RC224ATF   |         |                |         |         |

| Operating  | 30 mA   | 150 mW         | 32 mA   | 160 mW  |

| Sieep-Idle | 6 mA    | 30 mW          | 8 mA    | 40 mW   |

| Sleep-Stop | 0.4 mA  | 2 m <b>W</b>   | 1 mA    | 5 mW    |

Note: Input voltage ripple ≤ 0.1 volts peak-to-peak. The amplitude of any frequency between 20 kHz and 150 kHz must be less than 500 microvolts peak.

Table 7. Environmental Specifications

| Parameter            | Specification                                                                     |

|----------------------|-----------------------------------------------------------------------------------|

| OperatingTemperature | 0°C to +70°C (32°F to 158°F)                                                      |

| Storage Temperature  | - 55°C to +125°C (-67°F to +257°F)                                                |

| Relative Humidity    | Up to 90% noncondensing, or a wet bulb temperature up to 35°C, whichever is less. |

MD51R2-C1

5

### HARDWARE INTERFACE

The RC224ATF hardware interface signals are shown for the serial interface in Figure 1a, and for the parallel interface in Figure 1b.

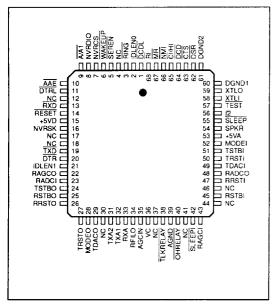

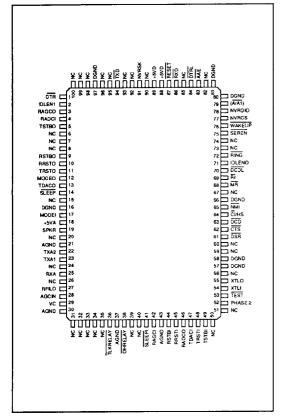

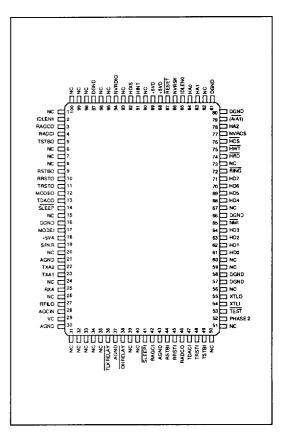

The RC224ATF 68-pin PLCC pinout diagrams are provided as Figures 2a and 2b for serial and parallel interface implementations, respectively. The 100-pin PQFP pinout diagrams are provided as Figures 3a and 3b for serial and parallel interface implementations, respectively.

RC224ATF 68-pin PLCC pin assignments are given in Tables 8a and 8b for serial and parallel interface

implementations, respectively. 100-pin PQFP pin assignments are given in Tables 9a and 9b for serial and parallel interface implementations, respectively.

The RC224ATF digital and analog characteristics are described in Tables 10 and 11, respectively.

The RC224ATF hardware interface signals are described in Table 12.

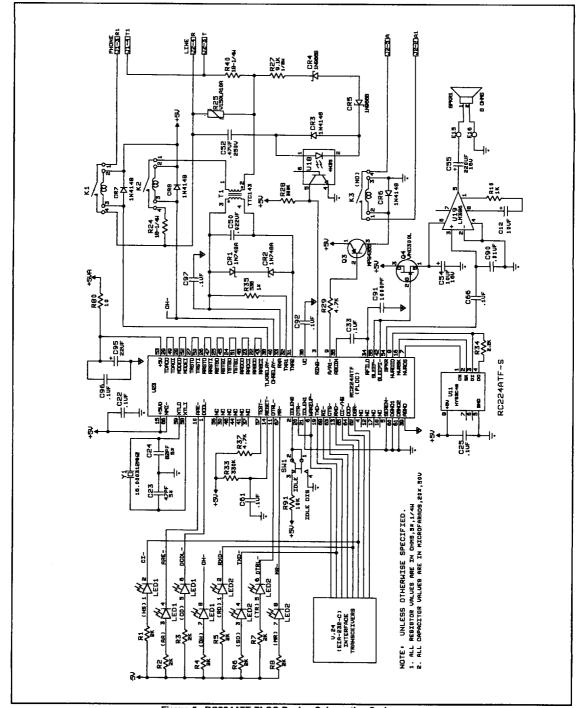

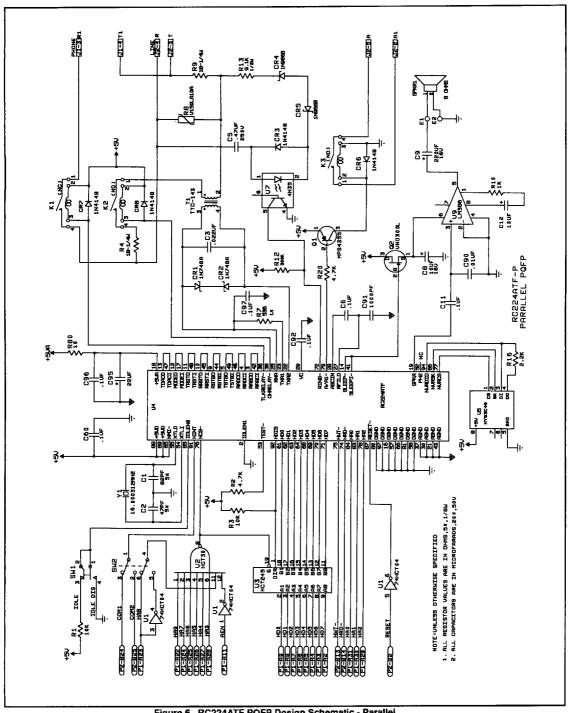

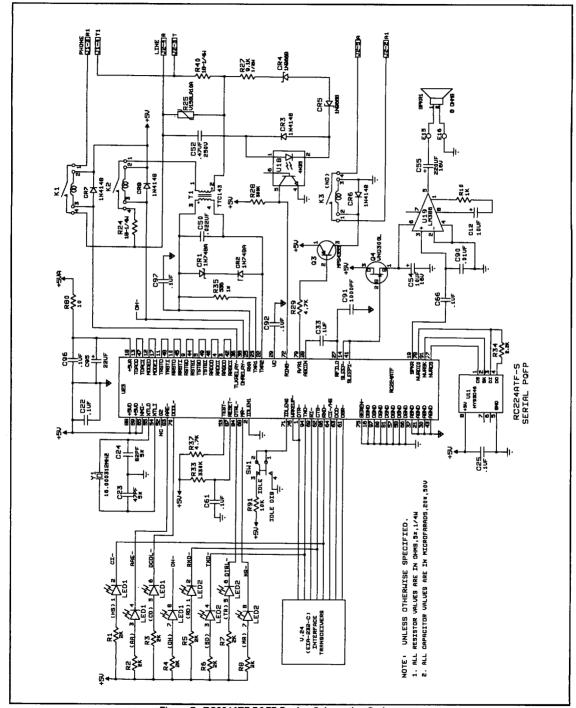

The parallel interface registers are identified in Table 13. Schematic designs using the RC224ATF in a 68-pin PLCC or 100-pin PQFP, implemented with either a parallel or serial interface, are found in Figures 4-7.

Figure 1a. RC224ATF Hardware Signals - Serial Interface

Figure 1b. RC224ATF Hardware Signals - Parallel Interface

Figure 2a. RC224ATF Pinouts - 68-Pin PLCC - Serial

Figure 2b. RC224ATF Pinouts - 68-Pin PLCC - Parallel

MD51R2-C2

8

### 2400 bps Single Device Data/Fax Modem with "AT" Commands

Table 8-a. RC224ATF PLCC Pin Assignments - Serial

| Pin Number | Signal Label          | I/O Type                   |

|------------|-----------------------|----------------------------|

| 1          | DCDL                  | OA                         |

| 2 3        | IDLEN0<br>RING        | IA<br>IA                   |

| 4          | NC NC                 | '^                         |

| 5          | SEREN                 | IA                         |

| 6 7        | WAKEUP                | IA.                        |

| 8          | NVRCS<br>NVRDIO       | OA<br>IA/OA                |

| ğ          | A/A1                  | OA                         |

| 10         | AAE                   | OA                         |

| 11<br>12   | DTRL<br>NC            |                            |

| 13         | RXD                   | OA                         |

| 14         | RESET                 | IC IC                      |

| 15         | +5VD<br>NVRSK         | To +5 VDC                  |

| 16<br>17   | NC NC                 | OA                         |

| 18         | NC                    |                            |

| 19         | TXD                   | IA                         |

| 20<br>21   | DTR<br>IDLEN1         | IA<br>IA                   |

| 22         | RAGCO                 | MI to RAGCI                |

| 23         | RADCI                 | MI to RADCO                |

| 24<br>25   | TSTBO<br>RSTBO        | MI to TSTBI                |

| 26<br>26   | RRSTO                 | MI to RSTBI<br>MI to RRSTI |

| 27         | TRSTO                 | MI to TRSTI                |

| 28         | MODEO                 | MI to MODEI                |

| 29<br>30   | TDACO<br>NC           | MI to TDACI                |

| 31         | TXA2                  | O(DD)                      |

| 32         | TXA1                  | O(DD)                      |

| 33<br>34   | RXA<br>RFILO          | I(DA)                      |

| 35         | AGCIN                 |                            |

| 36         | l vc                  |                            |

| 37<br>38   | NC<br>TLKRELAY        |                            |

| 39         | AGND                  | OD                         |

| 40         | OHRELAY               | OD                         |

| 41         | NC NC                 |                            |

| 42<br>43   | SLEEPI<br>RAGCI       | IA<br>MI to RAGCO          |

| 44         | NC NC                 |                            |

| 45         | RSTBI                 | MI to RSTBO                |

| 46<br>47   | NC<br>RRSTI           | MI to RRSTO                |

| 48         | RADCO                 | MI to RADCI                |

| 49         | TDACI                 | MI to TDACO                |

| 50<br>51   | TRSTI<br>TSTBI        | MI to TRSTO<br>MI to TSTBO |

| 52         | MODEI                 | MI to MODEO                |

| 53         | +5VA                  |                            |

| 54<br>55   | SPKR<br>SLEEP         | O(DF)<br>OA                |

| 56<br>56   | 02<br>02              | OA<br>OA                   |

| 57         | TEST                  | +5 VDC thru 4.7K           |

| 58<br>59   | XTLI<br>XTLO          | IE C                       |

| 60         | DGND1                 | OE                         |

| 61         | DGND2                 |                            |

| 62         | DSR                   | OA<br>OA                   |

| 63<br>64   | CTS<br>DCD            | OA<br>OA                   |

| 65         | CI/HS                 | OA .                       |

| 66         | NMI                   | To +5VDC                   |

| 67<br>68   | MR<br>RI              | OA<br>OA                   |

|            | Modem interconnection | UA UA                      |

Notes:

- 1. MI = Modern interconnection.

- NC = No external connection (may have internal connection), leave pin disconnected (open).

- 3. I/O Type: See Tables 10 (digital) and 11 (analog.)

Table 8-b. RC224ATF PLCC Pin Assignments - Parallel

| Din Number         | l Binari Labar   | 1 107                                    |

|--------------------|------------------|------------------------------------------|

| Pin Number         | Signal Label     | I/O Type                                 |

| 1 2                | HD6<br>HD7       | IA/OA<br>IA/OA                           |

| 3                  | RING             | I IAOA                                   |

| 4                  | HRD              | ΪÂ                                       |

| 5                  | <u>HWT</u>       | IA.                                      |

| 6<br>7             | HCS              | IA<br>OA                                 |

| 8                  | NVRCS<br>HA2     | OA<br>IA                                 |

| 9                  | A/A1             | ΙÖÀ                                      |

| 10                 | HA1              | l ia                                     |

| 11<br>12           | HA0              | ļ ļA                                     |

| 13                 | IDLEN0<br>NVRSK  | IA<br>OA                                 |

| 14                 | RESET            | ic                                       |

| 15                 | +5VD             | To +5 VDC                                |

| 16                 | HINT             | OA                                       |

| 17<br>18           | HDIS<br>NC       | OA                                       |

| 19                 | NVRDIO           | ia/oa                                    |

| 20                 | NC               | ,,,,,,                                   |

| 21                 | IDLEN1           | IA.                                      |

| 22<br>23           | RAGCO<br>RADCI   | MI to RAGCI<br>MI to RADCO               |

| 24                 | TSTBO            | MI to TSTBI                              |

| 25                 | RSTBO            | MI to RSTBI                              |

| 26                 | RRSTO            | MI to RRSTI                              |

| 27<br>28           | TRSTO            | MI to TRSTI                              |

| 28<br>29           | MODEO<br>TDACO   | MitoMODEI<br>MitoTDACI                   |

| 30                 | NC NC            | 1111 10 10 10 10 10 10 10 10 10 10 10 10 |

| 31                 | TXA2             | O(DD)                                    |

| 32<br>33           | TXA1             | O(DD)                                    |

| 33<br>34           | RXA<br>RFILO     | I(DA)                                    |

| 35                 | AGCIN            |                                          |

| 36                 | VC               |                                          |

| 37                 | NC<br>TUXPELAY   |                                          |

| 38<br>39           | TLKRĒLAY<br>AGND | OD                                       |

| 40                 | OHRELAY          | OD                                       |

| 41                 | NC               |                                          |

| 42<br>43           | SLEEPI           | IA .                                     |

| 43                 | RAGCI<br>NC      | MI to RAGCO                              |

| 45                 | RSTBI            | MitoRSTBO                                |

| 46                 | NC               |                                          |

| 47<br>48           | RRSTI            | MI to RRSTO                              |

| 48<br>49           | RADCO<br>TDACI   | MI to RADCI<br>MI to TDACO               |

| 50                 | TRSTI            | MI to TRSTO                              |

| 51                 | TSTBI            | MI to TSTBO                              |

| 52<br>53           | MODEI            | MI to MODEO                              |

| 53<br>54           | +5VA<br>SPKR     | O(DF)                                    |

| 55                 | SLEEP            | OA                                       |

| 56                 | o2<br>TEST       | OA                                       |

| 57<br>58           | I LSI            | +5 VDC thru 4.7K                         |

| 59                 | XTLI<br>XTLO     | IE<br>OE                                 |

| 60                 | DGND1            | "-                                       |

| 61                 | DGND2            |                                          |

| 62<br>63           | HD0<br>HD1       | IA/OA                                    |

| 63<br>64           | HD2              | IA/OA<br>IA/OA                           |

| 65                 | HD3              | IAOA                                     |

| 66                 | NMI .            | To +5VDC                                 |

| 67                 | HD4              | IA/OA                                    |

| 68<br>Notes: 1 Min | HD5              | IA/OA                                    |

Notes:

- 1. MI = Modern interconnection.

- NC = No external connection (may have internal connection), leave pin disconnected (open).

- 3. I/O Type: See Tables 10 (digital) and 11 (analog).

Figure 3a. RC224ATF Pinouts - 100-Pin PQFP - Serial

Figure 3b. RC224ATF Pinouts - 100-Pin PQFP - Parallel

### 2400 bps Single Device Data/Fax Modem with "AT" Commands

Table 9a. RC224ATF PQFP Pin Assignments - Serial

Pin Number Signal Label I/O Type DTR IΑ 2 **IDLEN1** IA **RAGCO** MI to RAGCI 4 RADCI MI to RADCO 5 **TSTBO** MI to TSTBI 6 7 NC NÇ 8 NC MI to RSTBI 9 RSTBO RRSTO 10 MI to RRSTI TRSTO MI to TRSTI 11 12 MODEO MI to MODEI TDACO SLEEP 13 MI to TDACI OA 15 NC 16 17 DGND DGND MODEL MI to MODEO +5VA 18 SPKR O(DF) 19 20 NC 21 22 AGND AGND TXA2 O(DD) 23 TXA1 O(DD) 24 NC 25 RXA I(DA) 26 27 NC RFILO 28 **AGCIN** 29 VC 30 AGND **AGND** 31 NC 32 NC 33 NC NC 35 NC TLKRELAY 36 OD 37 AGND OHRELAY AGND 38 39 NC 40 NC 41 SLEEPI IA MI to RAGCO RAGCI 43 AGND AGND 44 **RSTBI** MI to RSTBO 45 RRSTI MI to RRSTO 46 RADCO MI to RADCI 47 TDACI MI to TDACO 48 TRSTI MI to TRSTO 49 **TSTBI** MI to TSTBO 50 NC NC PHASE 2 OA TEST Note 4 XTLI ΙE 55 XTLO QΕ 56 57 NÇ DGND DGND 58 DGND DGND 59 NC NC

Table 9a. RC224ATF PQFP Pin Assignments - Serial (Cont'd)

| Pin Number | Signal Label | I/O Type |

|------------|--------------|----------|

| 61         | DSR<br>CTS   | OA       |

| 62         | CTS          | OA .     |

| 63         | DCD          | OA       |

| 64         | Cī/HS        | OA       |

| 65         | ЙМÍ          | Note 5   |

| 66         | DGND         | DGND     |

| 67         | NC           |          |

| 68         | NC<br>MR     | OA       |

| 69         | Ri           | OA       |

| 70         | DCDL         | OA       |

| 71         | IDLENO       | IA       |

| 72         | RING         | ΪA       |

| 73         | NC           |          |

| 74         | NC           |          |

| 75         | SEREN        | IA       |

| 76         | WAKEUP       | iA       |

| 77         | NVRCS        | ÖÄ       |

| 78         | NVRDIO       | IA/OA    |

| 79         | (A/A1)       | OA       |

| 80         | ÒGNÓ         | DGND     |

| 81         | DGND         | DGND     |

| 82         | NC           |          |

| 83         | ĀĀĒ          | OA       |

| 84         | DTAL         |          |

| 85         | NC           |          |

| 86         | RXD          | OA       |

| 87         | RESET        | IÇ       |

| 88         | +5VD         | Note 5   |

| 89         | +5VD         | Note 5   |

| 90         | NC           |          |

| 91         | NVRSK        | OA       |

| 92         | NC           | !        |

| 93         | NC           |          |

| 94         | TXD          | IA       |

| 95         | NC           |          |

| 96         | NC           |          |

| 97         | DGND         | DGND     |

| 98         | NC           |          |

| 99         | NC           |          |

| 100        | NC           |          |

| Nickon     |              |          |

Notes:

- 1. MI = Modern Interconnection.

- 2. NC = No connection (may have internal

- connection; leave pin disconnected (open)).

3. I/O types are described in Table 10 (digital

- signals) and Table 11 (analog signals).

- 4. Connect to +5 VDC through 4.7 K-ohms.

- 5. Connect to +5 VDC.

- 6. AGND is analog ground and DGND is digital ground.

11 MD51R2-C2

Table 9b. RC224ATF PQFP Pin Assignments - Parallel

| Pin Number                                                     | Signal Label                                                | I/O Type                                                                                              |

|----------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6                                     | NC IDLEN1 RAGCO RADCI TSTBO NC                              | IA<br>MI to RAGCI<br>MI to RADCO<br>MI to TSTBI                                                       |

| 8<br>9<br>10<br>11<br>12<br>13                                 | NC RSTBO RRSTO TRSTO MODEO TDACO SIEEP                      | MI to RSTBI<br>MI to RRSTI<br>MI to TRSTI<br>MI to MODEI<br>MI to TDACI<br>OA                         |

| 15<br>16<br>17<br>18                                           | NC<br>DGND<br>MODEI<br>+5VA                                 | DGND<br>MI to MODEO                                                                                   |

| 19<br>20                                                       | SPKR<br>NC<br>AGND                                          | O(DF)<br>AGND                                                                                         |

| 21<br>22<br>23<br>24                                           | TXA2<br>TXA1<br>NC                                          | O(DD)<br>O(DD)                                                                                        |

| 25<br>26                                                       | RXA<br>NC                                                   | I(DA)                                                                                                 |

| 27<br>28<br>29<br>30<br>31<br>32<br>33                         | RFILO<br>AGCIN<br>VC<br>AGND<br>NC<br>NC<br>NC              | AGND                                                                                                  |

| 34<br>35<br>36<br>37<br>38<br>39                               | NC<br>NC<br>TLKRELAY<br>AGND<br>OHRELAY<br>NC               | OD<br>AGND<br>OD                                                                                      |

| 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50 | NC SLEEPI RAGCI AGND RSTBI RRSTI RADCO TDACI TRSTI TSTBI NC | IA MI to RAGCO AGND MI to RSTBO MI to RRSTO MI to RADCI MI to TDACO MI to TRSTO MI to TSTO MI to TSTO |

| 51<br>52<br>53<br>54<br>55<br>56                               | NC<br>PHASE 2<br>TEST<br>XTLI<br>XTLO<br>NC                 | OA<br>Note 4<br>IE<br>OE                                                                              |

| 56<br>57<br>58<br>59<br>60                                     | NC<br>DGND<br>DGND<br>NC<br>NC                              | DGND<br>DGND                                                                                          |

Table 9b. RC224ATF PQFP Pin Assignments - Parallel (Contd)

| Pin Number | Signal Label | I/O Type |

|------------|--------------|----------|

| 61         | HD0          | IA/OA    |

| 62         | HD1          | IA/OA    |

| 63         | HD2          | IA/OA    |

| 64         | HD3          | IA/OA    |

| 65         | NMI          | Note 5   |

| 66         | DGND         | DGND     |

| 67         | NC NC        |          |

| 68         | HD4          | IA/OA    |

| 69         | HD5          | IA/OA    |

| 70         | HD6          | IA/OA    |

| 71         | HD7          | IA/OA    |

| 72         | RING         | iA.      |

| 73         | NC           |          |

| 74         | HRD          | IA       |

| 75         | HWT          | IA       |

| 76         | HCS          | IA       |

| 77         | NVRCS        | OA       |

| 78         | HA2          | ŀΑ       |

| 79         | (A/A1)       | OA       |

| 80         | ĎGNĎ         | DGND     |

| 81         | DGND         | DGND     |

| 82         | NC           |          |

| 83         | HA1          | IA       |

| 84         | HA0          | IA       |

| 85         | IDLENO       | IA       |

| 86         | NVRSK        | OA       |

| 87         | RESET        | IC       |

| 88         | +5VD         | Note 5   |

| 89         | +5VD         | Note 5   |

| 90         | NC           |          |

| 91         | HINT         | OA       |

| 92         | HDIS         | OA       |

| 93         | NC           |          |

| 94         | NVRDIO       | IA/OA    |

| 95         | NC           |          |

| 96         | NC           |          |

| 97         | DGND         | DGND     |

| 98         | NC           |          |

| 99         | NC           |          |

| 100        | NC           |          |

|            |              |          |

#### Notes:

12

- 1. MI = Modern Interconnection.

- 2. NC = No connection (may have internal connection; leave pin disconnected (open)).

- 3. I/O types are described in Table 10 (digital signals) and Table 11 (analog signals).

- Connect to +5 VDC through 4.7 K-ohms.

Connect to +5 VDC.

- 6. AGND is analog ground and DGND is digital ground.

MD51R2-C2

## 2400 bps Single Device Data/Fax Modem with "AT" Commands

Table 10. Digital Interface Characteristics

| Parameter                      | Symbol | Min. | Тур. | Max. | Units | Test Conditions <sup>1</sup>           |

|--------------------------------|--------|------|------|------|-------|----------------------------------------|

| Input High Voltage             | ViH    |      |      |      | Vdc   |                                        |

| Type IA                        |        | 2.0  | -    | Vcc  | 1     |                                        |

| Type IB                        |        | 2.4  | l –  | Vcc  | 1     |                                        |

| Type IC                        |        | 3.5  | _    | Vcc  |       |                                        |

| Type IE                        |        | -    | 4.0  |      |       | See Note 2.                            |

| Input Low Voltage              | VIL    | i    |      | l    | Vdc   |                                        |

| Types IA & IB                  |        | -0.3 | -    | 0.8  | 1     |                                        |

| Types IE                       |        | -    | 1.0  |      | 1     | See Note 2.                            |

| Input Leakage Current          | lin    | •    |      | ļ    | μAdc  |                                        |

| Type IA & IC (Non-multiplexed) |        | -    |      | ±10  | ] '   | V <sub>IN</sub> = 0 to V <sub>CC</sub> |

| Output High Voltage            | Vон    |      |      |      | Vdc   | · · · · · · · · · · · · · · · · · · ·  |

| Type OA [                      |        | 2.4  | _    |      |       | leoad = - 100 μA                       |

| Type OD                        |        |      | - 1  | Vcc  | 1     | ILOAD = 0 mA                           |

| Type OE                        |        |      | -    | _    | 1     | See Note 3.                            |

| Output Low Voltage             | Vol    |      |      |      | Vdc   |                                        |

| Type OA                        | . 02   | i _  | l _  | 0.4  | '**   | ILOAD = 1.6 mA                         |

| Type OD                        |        | _    | 0.75 | -    |       | ILOAD = 15 mA                          |

| Type OE                        |        | _    | -    | _    |       | See Note 3.                            |

| Three-State (Off)              | lтs    |      |      |      | μAdc  |                                        |

| Type OA                        | =      | -    | _    | ±25  | '"    | V <sub>IN</sub> = 0.8 V to 4.5 V       |

| RC224ATF Power Dissipation     | PD     |      |      |      | mW    | fin =16.00312 MHz @ XTLI               |

| Operating                      | -      | _    | 150  | 225  |       | ""                                     |

| Sieep - Idle                   |        | _    | 30   | 40   |       | I                                      |

| Sleep - Stop                   |        | _    | 2    | 5    | 1     | 4                                      |

Notes: 1. Test Conditions: V<sub>CC</sub> = 5V ± 5%, T<sub>A</sub> = 0°C to 70°C, (unless otherwise stated).

- 2. Type IE inputs are centered approximately 2.5 V and swing 1.5 VPEAK in each direction.

- 3. Type OE outputs provide oscillator feedback when operating with an external crystal.

Table 11. Analog Interface Characteristics

| Name       | Туре   | Characteristic                                                                        |                                                                       |  |  |  |  |

|------------|--------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| RXA        | I (DA) | Input Impedance:<br>Voltage Range:                                                    | > 50K-ohms<br>2.5 ± 1.6 V                                             |  |  |  |  |

| TXA1, TXA2 | O (DD) | Minimum Load: Maximum Capacitive Load: Output Impedance: Output Voltage: D.C. Offset: | 300 ohms<br>0.01μF<br>10 ohms<br>2.5 ± 1.6 V<br>< 200 mV <sup>1</sup> |  |  |  |  |

| SPKR       | O (DF) | Minimum Load: Maximum Capacitive Load: Output Impedance: Output Voltage: D.C. Offset: | 300 ohms<br>0.01 μF<br>10 ohms<br>2.5 ± 1.6 V<br>< 20 mV <sup>1</sup> |  |  |  |  |

Table 12. Hardware Interface Signal Definitions

| Label            | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |          | SYSTEM SIGNALS                                                                                                                                                                                                                                                                                                                                                                                       |

| XTLI<br>XTLO     | IE<br>OE | Crystal/Clock in and Crystal Out. The modern must be connected to an external crystal circuit consisting of a 16.000312 MHz crystal and two capacitors. Alternatively, XTLI may be driven with a buffered clock; in this case, XTLO should be left open.                                                                                                                                             |

| RESET            | IC       | Reset. The active low RESET input resets the internal modern logic. Upon RESET transitioning from high to low, modern operation returns to the state controlled by factory default values and stored values in NVRAM. During modern power turn-on, RESET must be held low for at least 5 ms after +5VD and +5VA operating voltage (see TSVD and +5VA below) is attained for the modern to stabilize. |

|                  |          | When the serial interface is selected, RESET can be connected to an external RC network to cause the modem to reset upon power turn on. When the parallel interface is selected, RESET should be connected to the host bus reset line.                                                                                                                                                               |

| SEREN            | IA       | Serial Interface Enable. When the SEREN input is low, serial interface is selected upon reset. In this case, the serial interface signals should be connected to the V.24 (EIA-232-D) Interface and LED indicators as shown in Figures 1a.                                                                                                                                                           |

| + 5VD<br>+ 5VA   | PWR      | + 5V Digital and Analog Supplies. +5V ±5% is required.                                                                                                                                                                                                                                                                                                                                               |

| DGND<br>AGND     | GND      | Digital and Analog Grounds.                                                                                                                                                                                                                                                                                                                                                                          |

|                  |          | SLEEP MODE SIGNALS                                                                                                                                                                                                                                                                                                                                                                                   |

| IDLENO<br>IDLEN1 | IA<br>IA | Idle Enable 0 and Idle Enable 1. Encoded inputs enable or disable the sleep modes as follows:                                                                                                                                                                                                                                                                                                        |

|                  |          | IDLEN1 IDLEN0 Mode  L L Idle mode disabled  L H Idle mode enabled  H L Stop mode disabled  H H Stop mode enabled                                                                                                                                                                                                                                                                                     |

|                  |          | If Idle option is enabled, the modem will enter idle mode after 5 seconds of inactivity (WAKEUP must also be high for the <u>serial interface</u> ). The modem will wakeup upon DTE activity (RXD for parallel mode and low on WAKEUP for serial mode) or the presence of RING.                                                                                                                      |

|                  |          | If Stop option is selected, the RING input becomes RING (i.e., the RING signal must be inverted). The modern will enter stop mode after 5 seconds of inactivity (and if WAKEUP is high for the serial interface). Only a 4 ms or longer pulse on the RING pin can wakup the modern from stop mode.                                                                                                   |

| SLEEP            | OA       | Sleep Mode. SLEEP output high indicates the modem is operating in its normal mode. SLEEP low indicates that the modem is in the sleep mode. The SLEEP output can also be used to control power to other devices.                                                                                                                                                                                     |

| SLEEPI           | IA       | Sleep Mode IA. SLEEP input low causes the integrated Analog (IA) to enter low power sleep mode.                                                                                                                                                                                                                                                                                                      |

| WAKEUP           | IA       | Wake Up. For serial interface only, WAKEUP input low removes the modem from the sleep mode (if in the sleep mode), or prevents the modem from entering the sleep mode (if not in the sleep mode). WAKEUP high allows the modem to enter sleep mode after 5 seconds of modem inactivity. WAKEUP is typically connected to DTR or TXD.                                                                 |

|                  |          | NVRAM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                      |

| NVRCS            | OA       | NVRAM Chip Select. NVRCS output high enables the NVRAM.                                                                                                                                                                                                                                                                                                                                              |

| NVRSK            | OA       | NVRAM Shiff Clock. The NVRSK output is used to shift data to or from the NVRAM.                                                                                                                                                                                                                                                                                                                      |

| NVRDIO           | IA/OA    | NVRAM Data In/NVRAM Data Out. NVRDIO is a bidirectional signal that carries both the serial input data from the NVRAM and the serial output data to the NVRAM. Depending on the specific NVRAM used, a resistor may be required between the NVRAM DO output pin and the modern NVRDIO bidirectional line. (Refer to the NVRAM data sheet).                                                           |

Table 12. Hardware Interface Signal Definitions (Cont'd)

| Label | I/O Type | Signal Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |          | SPEAKER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SPKR  | O(DF)    | Speaker Analog Output. The SPKR output reflects the output of the receive analog signal. The SPKR output is turned on or off by the Speaker Control Option (Mn command) and the gain is controlled by the Speaker Volume Option (Ln command). When the speaker is turned off, the SPKR output is clamped to the voltage at the VC pin. The SPKR output can drive a load as low as 300 ohms. Typically, the SPKR output is an input to an external LM386 audio power amplifier. |

|       |          | ASYNCHRONOUS SERIAL INTERFACE (SERIAL INTERFACE ONLY; SEREN = LOW)                                                                                                                                                                                                                                                                                                                                                                                                             |

| RXD   | OA       | Received Data. The modern presents received serial data to the $\overline{\text{RXD}}$ output pin.                                                                                                                                                                                                                                                                                                                                                                             |

| TXD   | IA       | Transmitted Data. The modem obtains serial data to be transmitted from the $\overrightarrow{TXD}$ input pin.                                                                                                                                                                                                                                                                                                                                                                   |

| DTŖ   | IA       | Data Terminal Ready. $\overline{\text{DTR}}$ input ON (low) indicates that the DTE is ready to operate. $\overline{\text{DTR}}$ input OFF (high) indicates that the DTE is not ready to operate.                                                                                                                                                                                                                                                                               |

| CTS   | OA       | Clear To Send. In data modes, the CTS output is ON; in fax modes, CTS is optionally used for flow control.                                                                                                                                                                                                                                                                                                                                                                     |

| DSR   | OA       | Data Set Ready. The DSR output is controlled by the AT&Sn command.                                                                                                                                                                                                                                                                                                                                                                                                             |

| DCD   | OA       | Data Carrier Detected. The DCD output is controlled by the AT&C command.                                                                                                                                                                                                                                                                                                                                                                                                       |

| CI/HS | OA       | Calling Indicator/High Speed Indicator. CI/HS output ON (low) indicates modem connection at 2400 bps.                                                                                                                                                                                                                                                                                                                                                                          |

| RI    | OA       | Ring Indicator. $\overline{\text{RI}}$ output ON (low) indicates the presence of an ON segment of a ring signal on the telephone line. (The ring signal cycle is typically two seconds ON, four seconds OFF.) The OFF (high) condition of the $\overline{\text{RI}}$ output is maintained during the OFF segment of the ring cycle (between rings) and at all other times when ringing is not being received.                                                                  |

|       |          | SERIAL INDICATOR INTERFACE (SERIAL INTERFACE ONLY; SEREN = LOW)                                                                                                                                                                                                                                                                                                                                                                                                                |

| AAE   | OA       | Auto Answer Enable. $\overline{AAE}$ output $\overline{ON}$ (low) indicates that modem auto answer mode has been enabled with the S0 = command. $\overline{AAE}$ high indicates auto answer has been disabled. The $\overline{AAE}$ output also indicates the status of the $\overline{RI}$ output.                                                                                                                                                                            |

| MR    | OA       | Modem Ready. $\overline{\text{MR}}$ output ON (low) indicates that the modem is ready, i.e., modem power is on and a test mode is not selected. In a test mode, the $\overline{\text{MR}}$ output pulses to indicate a test is in process.                                                                                                                                                                                                                                     |

| DCDL  | OA       | DCD Indicator. The DCDL output is controlled by the AT&C command.                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTRL  | OA       | DTR Indicator. The DTRL output is controlled by the AT&D command.                                                                                                                                                                                                                                                                                                                                                                                                              |

|       |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# 2400 bps Single Device Data/Fax Modem with "AT" Commands

Table 12. Hardware Interface Signal Definitions (Cont'd)

| Label                                                                                   | I/O Type | Signal Name/Description                                             |                                                                                                                                                                             |          |         |                                                                                                                 |  |  |  |  |  |

|-----------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                         |          | PARALLEI                                                            | . HOST                                                                                                                                                                      | INTER    | FACE (  | PARALLEL INTERFACE ONLY)                                                                                        |  |  |  |  |  |

|                                                                                         |          | (See Figure 1b.)                                                    |                                                                                                                                                                             |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          | When the I                                                          | When the HWT input signal is connected to the host bus write line, the parallel interface is                                                                                |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          | selected up                                                         | selected upon reset. (See Order No. 821 for waveform and timing information.)  The parallel interface emulates a 16C450 UART. Table 13 identifies the parallel interface    |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          |                                                                     |                                                                                                                                                                             |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          |                                                                     | registers. Parallel interface operation is equivalent to 16C450 operation with CS0 and CS1 inputs high and DISTR, DOSTR, and ADS inputs low. The corresponding RC224ATF and |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          |                                                                     |                                                                                                                                                                             |          |         | . 16C450 signals not required for RC224ATF host compute                                                         |  |  |  |  |  |

| operation are not shown.                                                                |          |                                                                     |                                                                                                                                                                             |          |         |                                                                                                                 |  |  |  |  |  |

|                                                                                         |          | -                                                                   | 6C450                                                                                                                                                                       | Signal   |         | RC224ATF Signal                                                                                                 |  |  |  |  |  |

|                                                                                         |          |                                                                     | A0 - /                                                                                                                                                                      |          |         | HAO - HA2                                                                                                       |  |  |  |  |  |

|                                                                                         |          |                                                                     | D0 -                                                                                                                                                                        | D7       |         | HD0 - HD7                                                                                                       |  |  |  |  |  |

|                                                                                         |          |                                                                     | MR<br>CS2                                                                                                                                                                   |          |         | RESET (Active low) HCS                                                                                          |  |  |  |  |  |

|                                                                                         |          |                                                                     | DIST                                                                                                                                                                        | Ŕ        |         | HWT                                                                                                             |  |  |  |  |  |

|                                                                                         |          |                                                                     | DOS                                                                                                                                                                         |          |         | HRD                                                                                                             |  |  |  |  |  |