# VSC8211 Datasheet

Single Port 10/100/1000BASE-T, 1000BASE-X, and 100BASE-FX PHY

## **1** General Description

VITESS

Ideally suited for Gigabit uplinks on Fast Ethernet switches, Fiber Optics, Media Converter applications, and GBIC/SFP modules, Vitesse's industry-leading low power VSC8211 integrates a high-performance 1.25Gbps SerDes and a triple speed (10/100/1000BASE-T) transceiver, providing unmatched tolerance to noise and cable plant imperfections.

Consuming approximately 700mW, the device requires only 3.3V and 1.2V power supplies. To further minimize system complexity and cost, the VSC8211's twisted pair interface features fully integrated line terminations, exceptionally low EMI, and robust Cable Sourced ESD (CESD) performance.

The VSC8211 provides systems designers with maximum design flexibility, offering direct connectivity to virtually any parallel or serial MAC, optical module, or triple speed GBIC/SFP connector. In addition to the familiar parallel MAC side interfaces (GMII, RGMII, MII, TBI, and RTBI), the device features two serial interfaces to minimize signal overhead: a 1000BASE-X compliant SerDes and SGMII. In 1000BASE-X

SerDes mode, the VSC8211 may be used to connect a MAC either to copper media (MAC to Cat-5) or to a 1000BASE-X optical module (MAC-to-Optics). In SGMII mode, the VSC8211 provides a fully compliant, 4 or 6-pin interface to MACs. The 1000BASE-X SerDes and SGMII interfaces offer either automatic or user-controlled auto-negotiation priority resolution between the 1000BASE-X and 1000BASE-T auto-negotiation processes. A single chip copper to optics Media Converter can be easily implemented by simultaneous use of the SerDes and Cat-5 media interfaces. This device also supports 100BASE-FX over its copper media interface.

To minimize power consumption, the VSC8211 offers several programmable power management modes meeting all Wakeon-LAN requirements. The device also supports Vitesse's comprehensive VeriPHY<sup>®</sup> Cable Diagnostics, offering the system manufacturer and IT administrator with a complete suite of cable plant diagnostics to simplify the manufacture, installation and management of Gigabit-over-copper networks.

## 2 Features and Benefits

| Features                                                                                                                                             | Benefits                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Very low power consumption                                                                                                                           | Reduces power supply costs                                                                                                                                              |

| <ul> <li>Supports PICMG 2.16 and 3.0 Ethernet backplanes at<br/>approximately 500mW</li> </ul>                                                       | Lowest power mode reduces power supply costs                                                                                                                            |

| <ul> <li>Patented line driver with integrated line side termination resistors</li> </ul>                                                             | <ul> <li>Allows use of simpler magnetic modules with up to 50%<br/>cost savings versus competition</li> </ul>                                                           |

|                                                                                                                                                      | <ul> <li>Saves over 12 components per port and reduces PCB<br/>area &amp; cost by fifty percent</li> </ul>                                                              |

| <ul> <li>Flexible MAC interfaces:<br/>Serial: SGMII &amp; SerDes</li> <li>Parallel: RGMII &amp; RTBI (2.5V &amp; 3.3V)<br/>GMII, MII, TBI</li> </ul> | <ul> <li>Serial: Connects to serial MACs or optical modules<br/>Supports copper GBIC/SFP modules</li> <li>Parallel: Connects to virtually any MAC controller</li> </ul> |

| User-programmable RGMII timing compensation                                                                                                          | Simplifies PCB layout, eliminating PCB trombones                                                                                                                        |

| High performance 1.25Gbps SerDes                                                                                                                     | <ul> <li>Supports CAT-5, fiber optic, and backplane interfaces<br/>from a single device</li> </ul>                                                                      |

|                                                                                                                                                      | <ul> <li>Suitable for dual media (copper &amp; fiber optics) switch<br/>ports, Gigabit uplinks on Fast Ethernet switches, GBICs/<br/>SFPs, LOM</li> </ul>               |

| <ul> <li>Auto-media Sense detects and configures to support<br/>fiber or copper</li> </ul>                                                           | Single chip solution for flexible media support                                                                                                                         |

| Features                                                                                                                                       | Benefits                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>User-configurable copper or fiber link selection<br/>preference with programmable interrupt and signal<br/>detect I/O pins</li> </ul> | Ensures plug-n-play link configuration when connected to any copper, fiber, or backplane link partner                                                                  |

| <ul> <li>Compliant with IEEE 802.3 (10BASE-T, 100BASE-TX,<br/>1000BASE-T, 1000BASE-X, 100BASE-FX) and SFP<br/>MSA specifications</li> </ul>    | <ul> <li>Ensures seamless deployment throughout copper and<br/>optical networks with industry's highest tolerance to<br/>noise and substandard cable plants</li> </ul> |

| Over 150m of Category-5 reach with industry's highest noise tolerance                                                                          | <ul> <li>Ensures trouble-free deployment in real world Ethernet<br/>networks</li> </ul>                                                                                |

| Several flexible power management modes                                                                                                        | <ul> <li>Reduces power consumption and system costs; fully<br/>compliant with Wake-on-LAN requirements</li> </ul>                                                      |

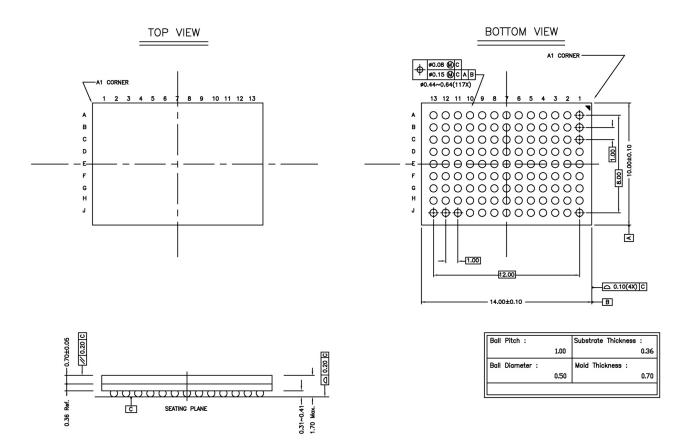

| Small footprint 10mm x 14mm, 117-LBGA package                                                                                                  | <ul> <li>Suitable for Gigabit switch ports, GBICs/SFPs, media<br/>converters</li> </ul>                                                                                |

|                                                                                                                                                |                                                                                                                                                                        |

# 3 Applications

- Dual Media Switch Ports

- iSCSI and TOE LOM

- Media Converters

- Triple-speed GBIC/SFP modules

- Backplanes

# 4 Application Diagrams

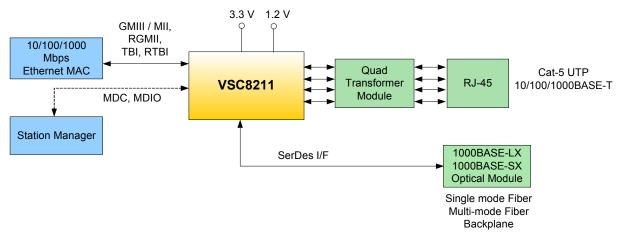

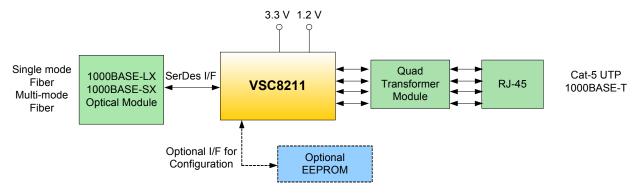

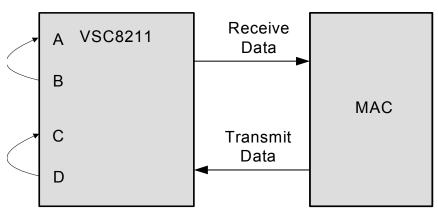

Figure 1. Parallel MAC to Cat-5, Fiber Optics, or Backplanes

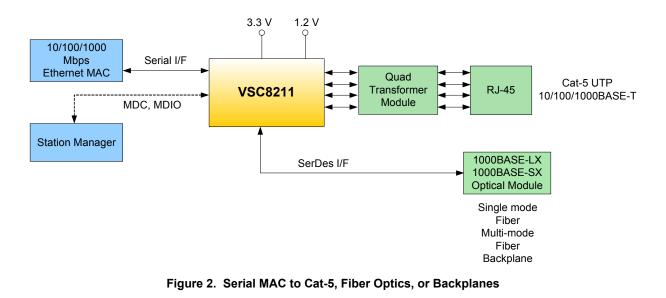

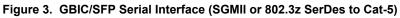

Figure 4. Media Converter (1000BASE-X to Cat-5)

Downloaded by spatni@partminer.com on November 22, 2006 from Vitesse.com

# Contents

| 1  | General Description1 |           |                                                              |    |

|----|----------------------|-----------|--------------------------------------------------------------|----|

| 2  | Featu                | ures and  | Benefits                                                     | 1  |

| 3  | Applications         |           |                                                              |    |

| 4  | Application Diagrams |           |                                                              |    |

|    |                      |           |                                                              |    |

| 5  |                      | -         | cifications & Documentation                                  |    |

| 6  | Datas                | sheet Co  | nventions                                                    | 15 |

| 7  | Docu                 | iment His | story and Notices                                            |    |

| 8  | Devi                 | ce Block  | Diagram                                                      | 17 |

| 9  | Pack                 | age Pin / | Assignments & Signal Descriptions                            |    |

|    | 9.1                  | -         | 11 117-Ball LBGA Package Ball Diagram                        |    |

|    | 9.2                  |           | Ball to Signal Name Cross Reference                          |    |

|    | 9.3                  |           | Type Description                                             |    |

|    | 9.4                  | U U       | d Pin Descriptions                                           |    |

|    | ••••                 | 9.4.1     | Configuration and Control Signals                            |    |

|    |                      | 9.4.2     | System Clock Interface Signals (SCI)                         |    |

|    |                      | 9.4.3     | Analog Bias Signals                                          |    |

|    |                      | 9.4.4     | JTAG Access Port                                             |    |

|    |                      | 9.4.5     | Serial Management Interface Signals                          |    |

|    |                      | 9.4.6     | EEPROM Interface Signals                                     | 25 |

|    |                      | 9.4.7     | LED Interface Signals                                        | 25 |

|    |                      | 9.4.8     | Parallel MAC Interface Signals - Transmit Signals            | 26 |

|    |                      | 9.4.9     | Parallel MAC Interface Signals - Receive Signals             | 28 |

|    |                      | 9.4.10    | Serial MAC/Media Interface Signals                           |    |

|    |                      | 9.4.11    | Twisted Pair Interface Signals                               |    |

|    |                      | 9.4.12    | Power Supply and Ground Connections                          |    |

|    |                      | 9.4.13    | No Connects                                                  |    |

|    | 9.5                  | Power     | Supply and Associated Functional Signals                     |    |

| 10 | Syste                | em Sche   | matics                                                       |    |

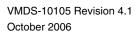

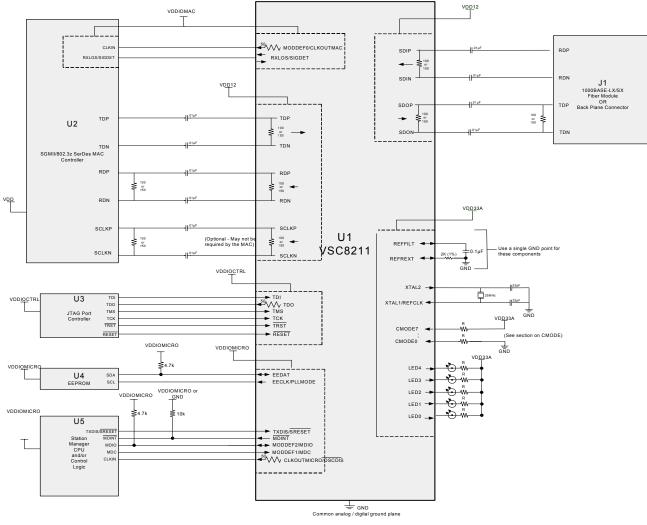

|    | 10.1                 | Parallel  | Data MAC to CAT5 Media PHY Operating Mode                    |    |

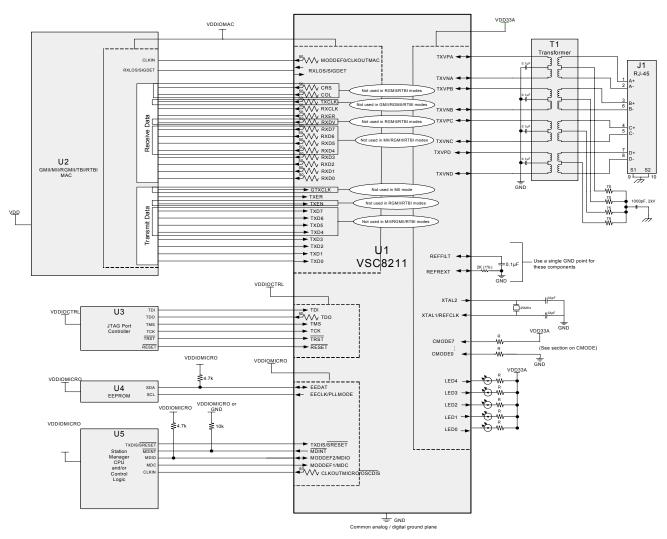

|    | 10.2                 | Parallel  | Data MAC to 1000Mbps Fiber Media PHY Operating Mode          |    |

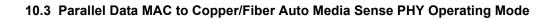

|    | 10.3                 | Parallel  | Data MAC to Copper/Fiber Auto Media Sense PHY Operating Mode |    |

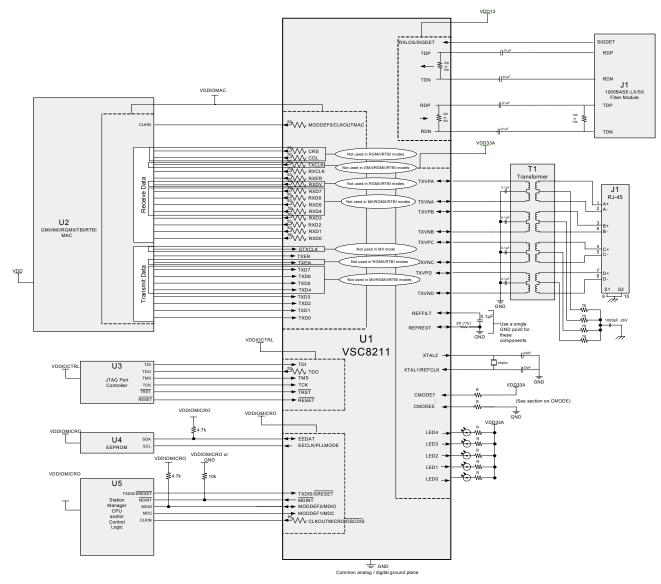

|    | 10.4                 | SGMII/8   | 802.3z SerDes MAC to CAT5 Media PHY Operating Mode           |    |

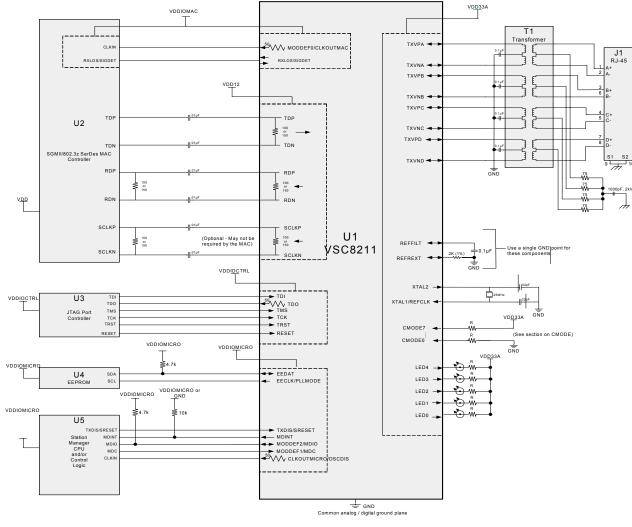

|    | 10.5                 | SGMII/8   | 802.3z SerDes to 1000Mbps Fiber Media PHY Operating Mode     |    |

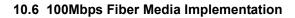

|    | 10.6                 | 100Mbp    | os Fiber Media Implementation                                | 41 |

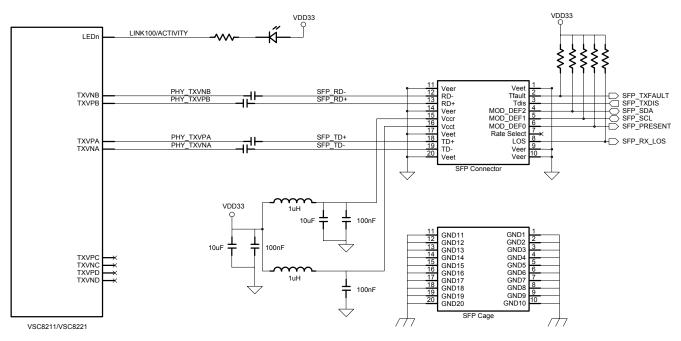

|    | 10.7                 | Serial N  | AC to Fiber/CAT5 Media PHY Operating Mode                    |    |

| 11 | Twist | ed Pair Interface                                                |    |

|----|-------|------------------------------------------------------------------|----|

|    | 11.1  | Twisted Pair Autonegotiation (IEEE802.3 Clause 28)               |    |

|    | 11.2  | Twisted Pair Auto MDI/MDI-X Function                             |    |

|    | 11.3  | Auto MDI/MDI-X in Forced 10/100 Link Speeds                      |    |

|    | 11.4  | Twisted Pair Link Speed Downshift                                |    |

|    | 11.5  | 100Mbps Fiber Support Over Copper Media Interface                |    |

|    |       | 11.5.1 Register Settings                                         | 45 |

| 12 | Trans | sformerless Operation for PICMG 2.16 and 3.0 IP-based Backplanes |    |

| 13 | Dual  | Mode Serial Management Interface (SMI)                           |    |

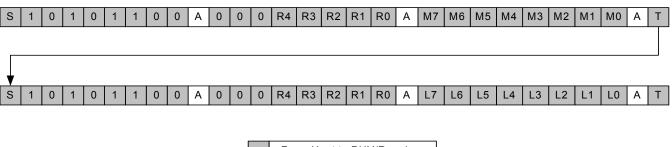

|    | 13.1  | PHY Register Access with SMI in MSA mode                         |    |

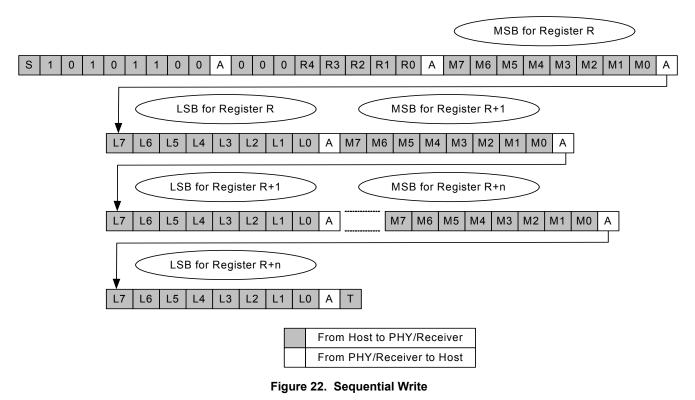

|    |       | 13.1.1 Write Operation - Random Write                            | 48 |

|    |       | 13.1.2 Write Operation - Sequential Write                        | 49 |

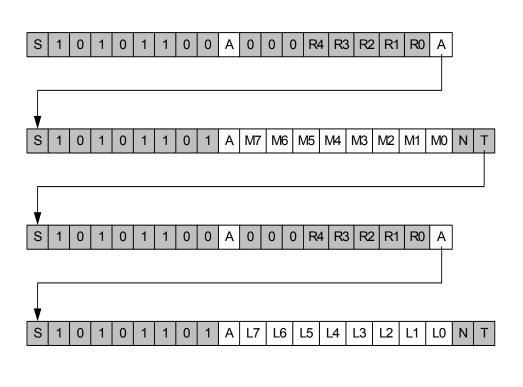

|    |       | 13.1.3 Read Operation - Random Read                              |    |

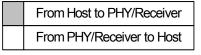

|    |       | 13.1.4 Read Operation - Sequential Read                          |    |

|    |       | PHY Register Access with SMI in IEEE Mode                        |    |

|    | 13.3  | SMI Interrupt                                                    | 53 |

| 14 | LED   | Interface                                                        |    |

|    | 14.1  | Serial LED Output                                                | 56 |

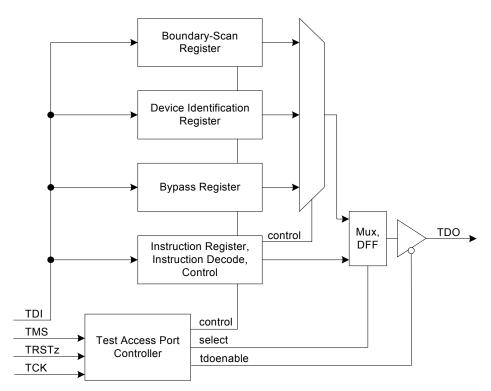

| 15 | Test  | Mode Interface (JTAG)                                            | 57 |

|    | 15.1  | Supported Instructions and Instruction Codes                     | 58 |

|    | 15.2  | Boundary-Scan Register Cell Order                                | 59 |

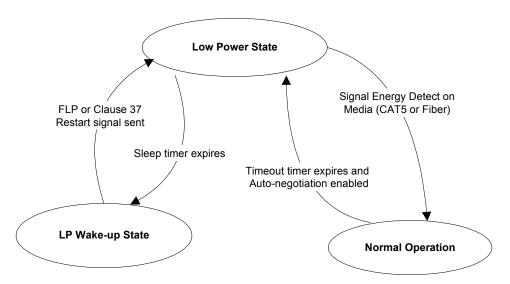

| 16 | Enha  | nced ActiPHY Power Management                                    | 60 |

|    | 16.1  | Operation in Enhanced ActiPHY Mode                               | 60 |

|    | 16.2  | Low power state                                                  | 61 |

|    | 16.3  | LP Wake up state                                                 | 61 |

|    | 16.4  | Normal operating state                                           | 61 |

| 17 | Ethe  | met In-line Powered Device Support                               |    |

|    | 17.1  | Cisco In-Line Powered Device Detection                           |    |

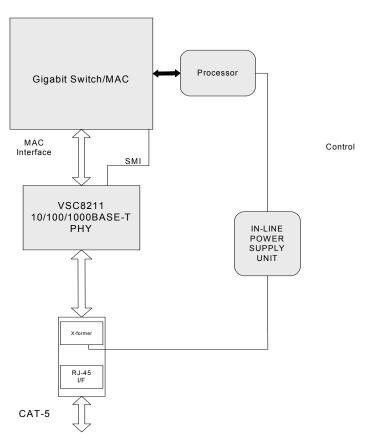

|    | 17.2  | In-Line Power Ethernet Switch Diagram                            |    |

|    | 17.3  | In-Line Powered Device Detection (Cisco Method)                  | 62 |

|    | 17.4  | IEEE 802.3af (DTE Power via MDI)                                 |    |

| 18 | Adva  | nced Test Modes                                                  | 64 |

|    | 18.1  | 1000BASE-T Ethernet Packet Generator (EPG)                       |    |

|    | 18.2  | 1000BASE-T CRC Counter                                           | 64 |

|    | 18.3  | Far-end Loopback                                                 | 64 |

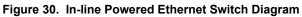

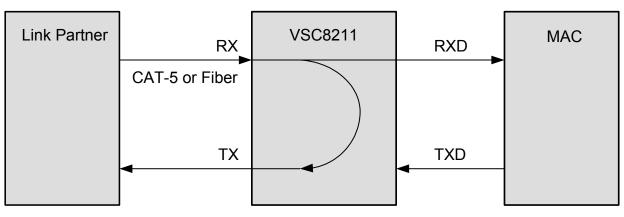

|    | 18.4  | Near-end Loopback                                                | 64 |

|    |       | Connector Loopback                                               |    |

### VSC8211 Datasheet

| 19 | Hard | ware Conf          | iguration Using CMODE Pins                                                                                                                    | 66  |

|----|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 19.1 | Setting th         | e CMODE Configuration Bits                                                                                                                    | 66  |

|    | 19.2 | CMODE              | Bit descriptions                                                                                                                              | 66  |

|    | 19.3 | Procedur           | e For Selecting CMODE Pin Pull-up/Pull-down Resistor Values                                                                                   | 71  |

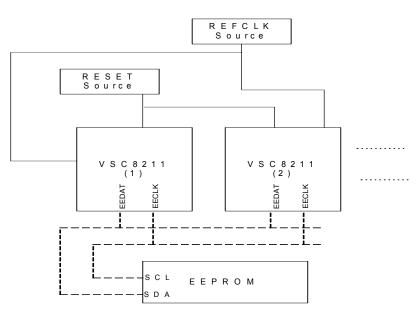

| 20 | EEPF | ROM Interf         | ace                                                                                                                                           | 72  |

|    | 20.1 | Program            | ning Multiple VSC8211s Using the Same EEPROM                                                                                                  | 73  |

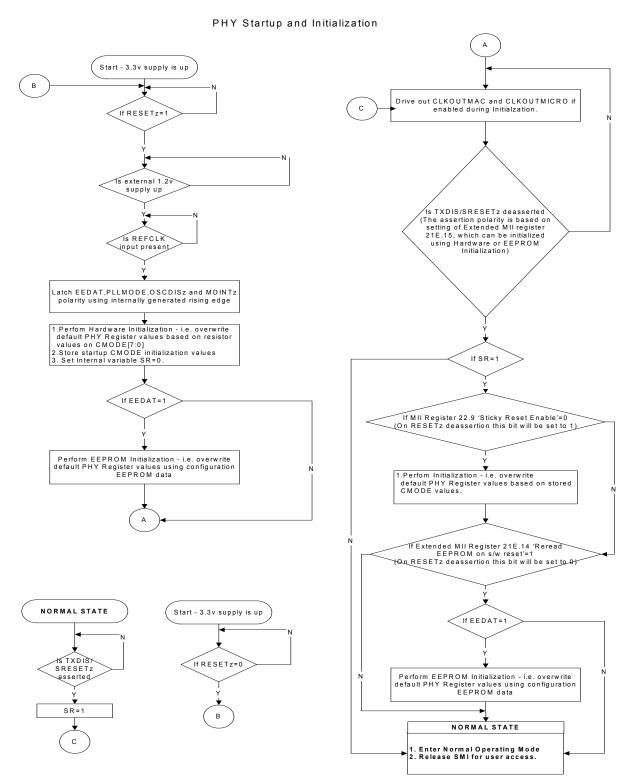

| 21 | PHY  | Startup an         | d Initialization                                                                                                                              | 75  |

| 22 | PHY  | Operating          | Modes                                                                                                                                         | 76  |

|    | 22.1 | PHY Ope            | erating Mode Description                                                                                                                      | 76  |

|    |      | 22.1.1             | Auto Media Sense (AMS) Media Interface PHY Operating Modes                                                                                    | 76  |

|    |      | 22.1.2             | Serial MAC to Serial Media PHY Operating Mode:                                                                                                | 77  |

| 23 | IEEE | 802.3 Clau         | se 28/37 Remote Fault Indication Support                                                                                                      | 77  |

| 24 | PHY  | Register S         | et Conventions                                                                                                                                | 80  |

|    | 24.1 | PHY's Re           | egister Set Structure                                                                                                                         | 80  |

|    | 24.2 | PHY's Re           | egister Set Nomenclature                                                                                                                      | 81  |

|    | 24.3 | PHY Reg            | lister Bit Types                                                                                                                              | 81  |

| 25 | PHY  | Register S         | et                                                                                                                                            | 82  |

|    | 25.1 | Clause 2           | 8/37 Resister View                                                                                                                            | 82  |

|    | 25.2 | PHY Reg            | ister Names and Addresses                                                                                                                     | 83  |

|    | 25.3 | MII Regis          | ster Descriptions                                                                                                                             | 85  |

|    |      | 25.3.1             | Register 0 (00h) – Mode Control Register - Clause 28/37 View                                                                                  | 85  |

|    |      | 25.3.2             | Register 1 (01h) – Mode Status Register - Clause 28/37 View                                                                                   |     |

|    |      | 25.3.3             | Register 2 (02h) – PHY Identifier Register #1 - Clause 28/37 View                                                                             |     |

|    |      | 25.3.4             | Register 3 (03h) – PHY Identifier Register #2 - Clause 28/37 View                                                                             |     |

|    |      | 25.3.5             | Register 4 (04h) – Auto-Negotiation Advertisement Register                                                                                    |     |

|    |      | 25.3.6<br>25.3.7   | Register 5 (05h) – Auto-Negotiation Link Partner Ability Register                                                                             |     |

|    |      | 25.3.7             | Register 6 (06h) – Auto-Negotiation Expansion Register<br>Register 7 (07h) – Auto-Negotiation Next-Page Transmit Register - Clause 28/37 View |     |

|    |      | 25.3.9             | Register 8 (08h)–Auto-Negotiation Link Partner Next-Page Receive Register, Clause 28/37 V                                                     |     |

|    |      | 25.3.10            | Register 9 (09h) – 1000BASE-T Control Register                                                                                                |     |

|    |      | 25.3.11            | Register 10 (0Ah) – 1000BASE-T Status Register #1                                                                                             |     |

|    |      | 25.3.12            | Register 11 (0Bh) – Reserved Register                                                                                                         |     |

|    |      | 25.3.13            | Register 12 (0Ch) – Reserved Register                                                                                                         | 100 |

|    |      | 25.3.14            | Register 13 (0Dh) – Reserved Register                                                                                                         | 100 |

|    |      | 25.3.15            | Register 14 (0Eh) – Reserved Register                                                                                                         |     |

|    |      | 25.3.16            | Register 15 (0Fh) – 1000BASE-T Status Register #2                                                                                             |     |

|    |      | 25.3.17            | Register 16 (10h) – Reserved                                                                                                                  |     |

|    |      | 25.3.18            | Register 17 (11h) – Reserved                                                                                                                  |     |

|    |      | 25.3.19<br>25.3.20 | Register 18 (12h) – Bypass Control Register<br>Register 19 (13h) – Reserved                                                                   |     |

|    |      | 20.0.20            |                                                                                                                                               | 105 |

|    |       | 25.3.21     | Register 20 (14h) – Reserved                                                 | 105 |

|----|-------|-------------|------------------------------------------------------------------------------|-----|

|    |       | 25.3.22     | Register 21 (15h) – Reserved                                                 |     |

|    |       | 25.3.23     | Register 22 (16h) – Control & Status Register                                |     |

|    |       | 25.3.24     | Register 23 (17h) – PHY Control Register #1                                  |     |

|    |       | 25.3.25     | Register 24 (18h) – PHY Control Register #2                                  |     |

|    |       | 25.3.26     | Register 25 (19h) – Interrupt Mask Register                                  |     |

|    |       | 25.3.27     | Register 26 (1Ah) – Interrupt Status Register                                |     |

|    |       | 25.3.28     | Register 27 (1Bh) – LED Control Register                                     | 117 |

|    |       | 25.3.29     | Register 28 (1Ch) – Auxiliary Control & Status Register                      | 119 |

|    |       | 25.3.30     | Register 29 (1Dh) – Reserved                                                 | 120 |

|    |       | 25.3.31     | Register 30 (1Eh) - MAC Interface Clause 37 Autonegotiation Control & Status | 120 |

|    |       | 25.3.32     | Register 31 (1Fh) – Extended Page Access                                     | 122 |

|    | 25.4  | Extended    | I MII Registers                                                              | 123 |

|    |       | 25.4.1      | Register 16E (10h) - Fiber Media Clause 37 Autonegotiation Control & Status  | 123 |

|    |       | 25.4.2      | Register 17E (11h) - Serdes Control Register                                 | 124 |

|    |       | 25.4.3      | Register 18E (12h) - Reserved                                                | 125 |

|    |       | 25.4.4      | Register 19E (13h) - SerDes Control Register # 2                             | 125 |

|    |       | 25.4.5      | Register 20E (14h) - Extended PHY Control Register #3                        | 126 |

|    |       | 25.4.6      | Register 21E (15h) - EEPROM Interface Status and Control Register            | 128 |

|    |       | 25.4.7      | Register 22E (16h) - EEPROM Data Read/Write Register                         | 129 |

|    |       | 25.4.8      | Register 23E (17h) - Extended PHY Control Register #4                        |     |

|    |       | 25.4.9      | Register 24E (18h) - Reserved                                                |     |

|    |       | 25.4.10     | Register 25E (19h) - Reserved                                                |     |

|    |       | 25.4.11     | Register 26E (1Ah) - Reserved                                                |     |

|    |       | 25.4.12     | Register 27E (1Bh) - Reserved                                                |     |

|    |       | 25.4.13     | Register 28E (1Ch) - Reserved                                                |     |

|    |       | 25.4.14     | Register 29E (1Dh) - 1000BASE-T Ethernet Packet Generator (EPG) Register #1  |     |

|    |       | 25.4.15     | Register 30E (1Eh) - 1000BASE-T Packet Generator Register #2                 | 132 |

| 26 | Elect | rical Speci | ifications                                                                   | 133 |

|    | 26.1  | Absolute    | Maximum Ratings                                                              | 133 |

|    |       |             | ended Operating Conditions                                                   |     |

|    |       |             | Application Data                                                             |     |

|    |       |             |                                                                              |     |

|    |       | -           | Thermal Specifications - 117 LBGA                                            |     |

|    | 26.5  | Current a   | nd Power Consumption                                                         | 136 |

| 27 | DC S  | pecificatio | ns                                                                           | 141 |

|    | 27.1  | Digital Pir | ns (VDDIO = 3.3V)                                                            | 141 |

|    | 27.2  | Digital Pir | ns (VDDIO = 2.5V)                                                            | 141 |

|    |       | •           |                                                                              |     |

| 28 | Clock | king Speci  | fications                                                                    | 142 |

|    |       |             | e Clock Option                                                               |     |

|    |       |             | ption                                                                        |     |

|    | 20.2  | Orystar O   | 2001                                                                         |     |

| 29 | SerDes Specifications                                                | . 144 |

|----|----------------------------------------------------------------------|-------|

| 30 | System Timing Specifications                                         | . 145 |

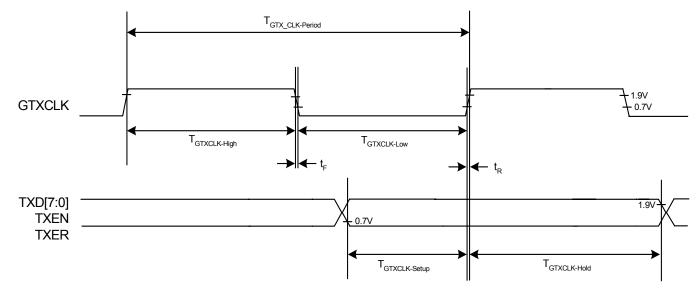

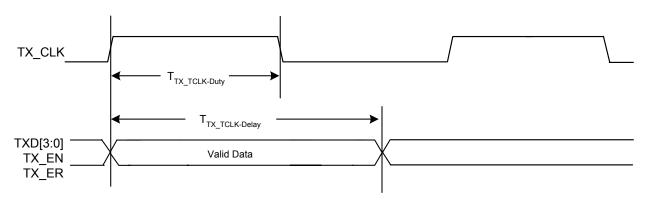

|    | 30.1 GMII Mode Transmit Timing (1000BASE-T)                          | . 145 |

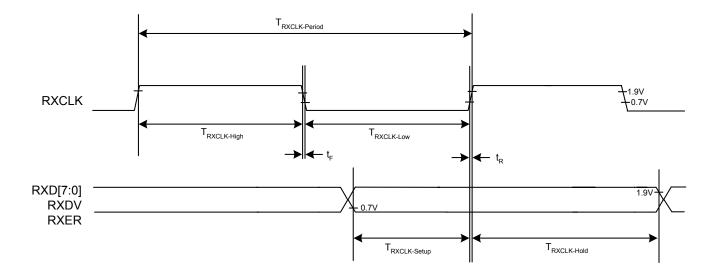

|    | 30.2 GMII Mode Receive Timing (1000BASE-T)                           | . 146 |

|    | 30.3 MII Transmit Timing (100Mbps)                                   | . 147 |

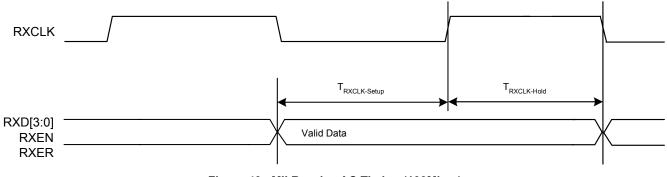

|    | 30.4 MII Receive Timing (100Mbps)                                    | . 147 |

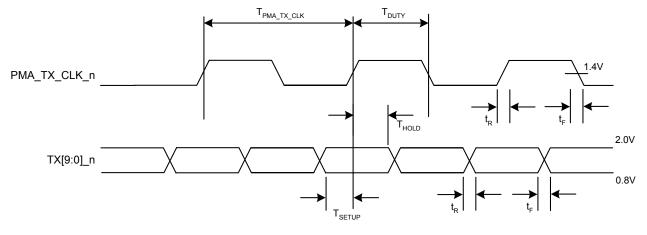

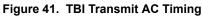

|    | 30.5 TBI Mode Transmit Timing                                        | . 148 |

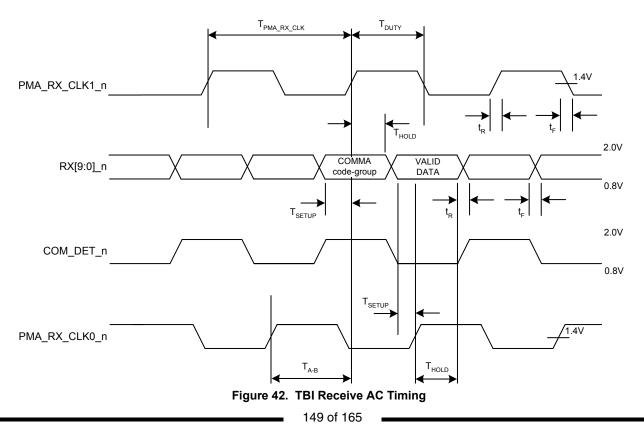

|    | 30.6 TBI Mode Receive Timing                                         | . 149 |

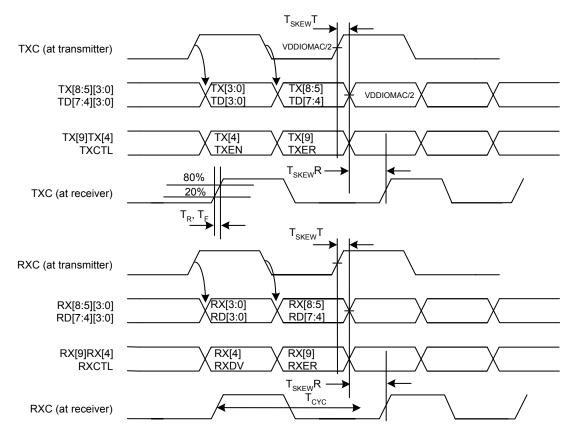

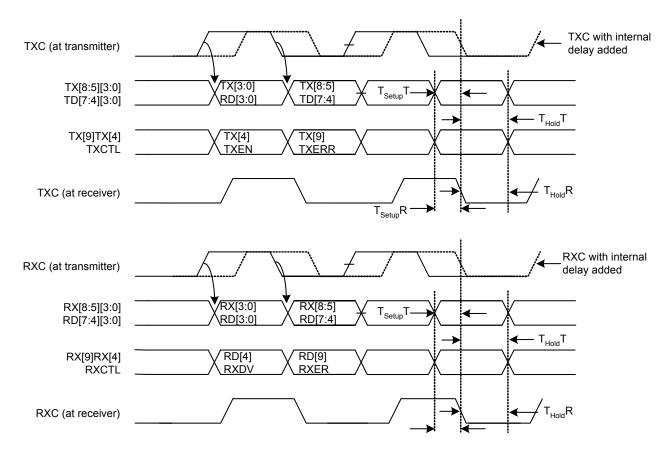

|    | 30.7 RGMII/RTBI Mode Timing                                          | . 150 |

|    | 30.8 JTAG Timing                                                     | . 153 |

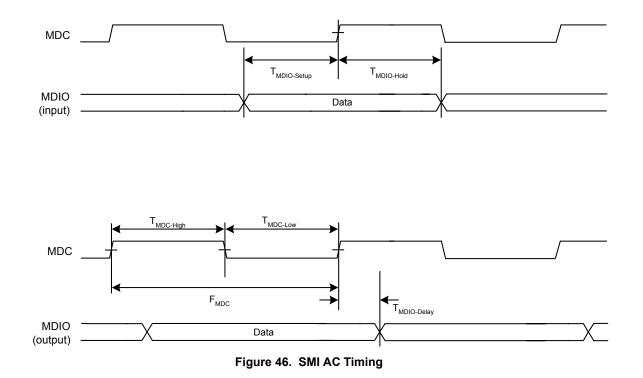

|    | 30.9 SMI Timing                                                      | . 154 |

|    | 30.10 MDINT Timing                                                   | . 155 |

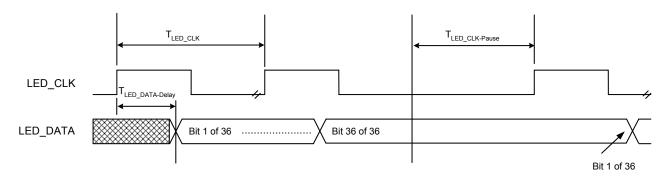

|    | 30.11 Serial LED_CLK and LED_DATA Timing                             |       |

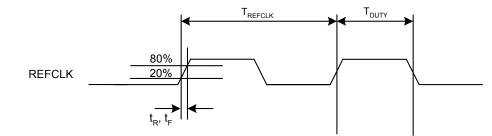

|    | 30.12 REFCLK Timing                                                  |       |

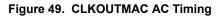

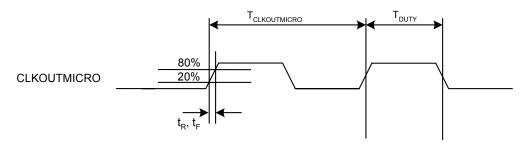

|    | 30.13 CLKOUTMAC and CLKOUTMICRO Timing                               |       |

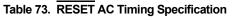

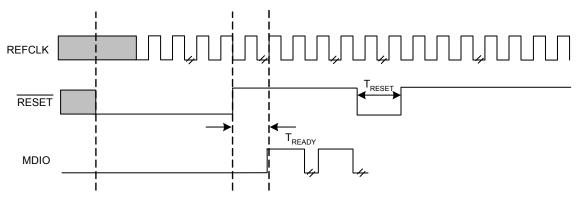

|    | 30.14 Reset Timing                                                   | . 158 |

| 31 | Packaging Specifications                                             | . 159 |

|    | 31.1 Package Moisture Sensitivity                                    | . 159 |

| 32 | Ordering Information                                                 | . 160 |

|    | 32.1 Devices                                                         | . 160 |

| 33 | Design Guidelines                                                    | . 161 |

|    | 33.1 Required PHY Register Write Sequence                            | . 161 |

|    | 33.2 Interoperability with Intel 82547EI Gigabit Ethernet MAC+PHY IC | . 161 |

|    | 33.3 SerDes Jitter                                                   | . 161 |

|    | 33.4 100BASE-FX Initialization Script                                | . 162 |

| 34 | Product Support                                                      | . 165 |

|    | 34.1 Available Documents and Application Notes                       | . 165 |

# Figures

| Figure 1.  | Parallel MAC to Cat-5, Fiber Optics, or Backplanes                                         | 3    |

|------------|--------------------------------------------------------------------------------------------|------|

| Figure 2.  | Serial MAC to Cat-5, Fiber Optics, or Backplanes                                           |      |

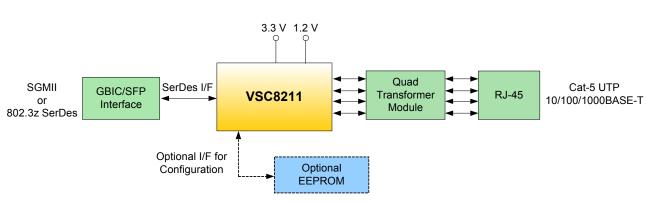

| Figure 3.  | GBIC/SFP Serial Interface (SGMII or 802.3z SerDes to Cat-5)                                |      |

| Figure 4.  | Media Converter (1000BASE-X to Cat-5)                                                      | 4    |

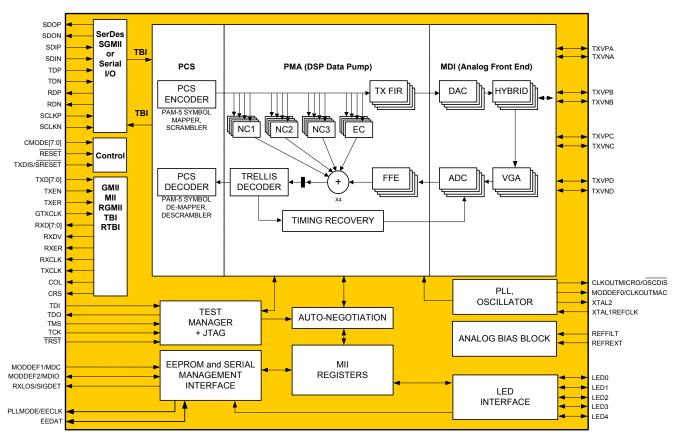

| Figure 5.  | VSC8211 Block Diagram                                                                      | . 17 |

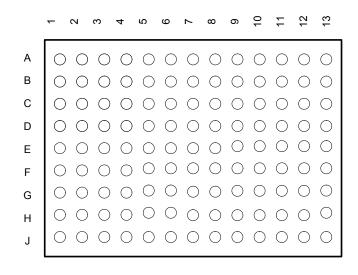

| Figure 6.  | VSC8211 117 Ball LBGA Package Ball Diagram18                                               |      |

| Figure 7.  | 117-Ball LBGA Signal Map (top view)19                                                      |      |

| Figure 8.  | System Schematic - 'Parallel Data MAC to CAT5 Media' PHY Operating Mode                    |      |

| Figure 9.  | System Schematic - 'Parallel Data MAC to 1000Mbps Fiber Media' PHY Operating Mode          | . 37 |

| Figure 10. | System Schematic - 'Parallel Data MAC to Copper/Fiber Auto Media Sense' PHY Operating Mode | . 38 |

| Figure 11. | System Schematic - 'SGMII/802.3z SerDes MAC to CAT5 Media' PHY Operating Mode              | . 39 |

| Figure 12. | System Schematic - 'SGMII/802.3z SerDes to 1000Mbps Fiber Media' PHY Operating Mode        | . 40 |

| Figure 13. | System Schematic – '100Mbps Fiber Media' Implementation                                    | . 41 |

| Figure 14. | System Schematic - 'Serial MAC to Fiber/CAT5 Media' PHY Operating Mode                     | . 42 |

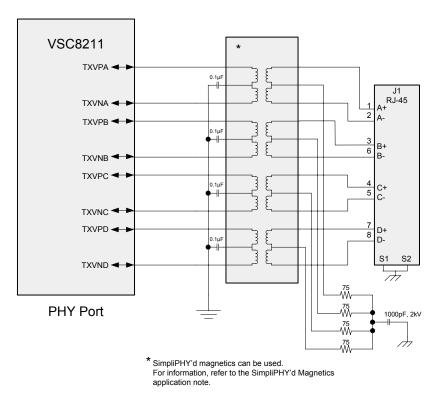

| Figure 15. | VSC8211 Twisted Pair Interface                                                             | . 43 |

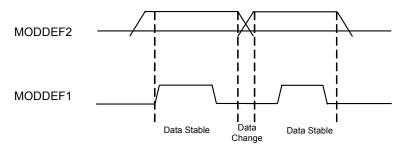

| Figure 16. | Data Validity                                                                              | . 46 |

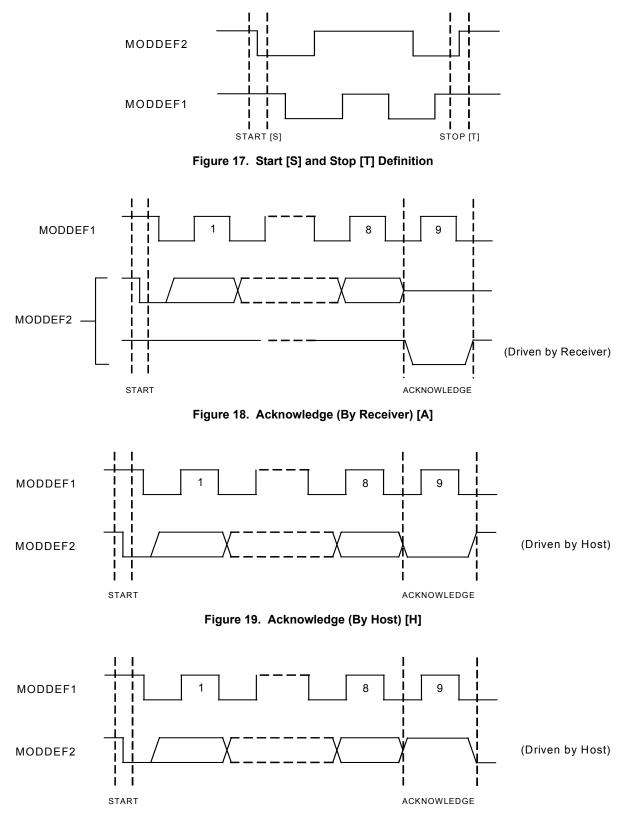

| Figure 17. | Start [S] and Stop [T] Definition                                                          | . 47 |

| Figure 18. | Acknowledge (By Receiver) [A]                                                              | . 47 |

| Figure 19. | Acknowledge (By Host) [H]                                                                  | . 47 |

| Figure 20. | No Acknowledge (By Host) [N] 47                                                            |      |

| Figure 21. | Random Write                                                                               | . 48 |

| Figure 22. | Sequential Write                                                                           |      |

| Figure 23. | Random Read                                                                                |      |

| Figure 24. | Sequential Read                                                                            | . 51 |

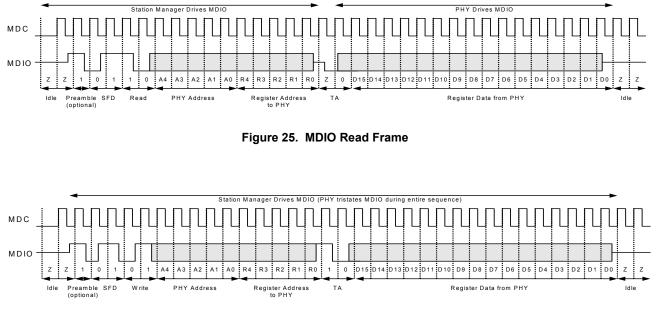

| Figure 25. | MDIO Read Frame                                                                            | . 53 |

| Figure 26. | MDIO Write Frame                                                                           | . 53 |

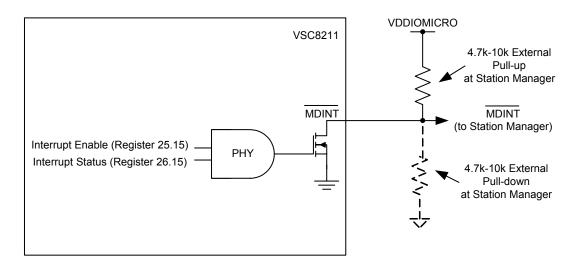

| Figure 27. | Logical Representation of MDINT Pin                                                        | . 53 |

| Figure 28. | Test Access Port and Boundary Scan Architecture                                            | . 57 |

| Figure 29. | Enhanced ActiPHY State Diagram                                                             | . 60 |

| Figure 30. | In-line Powered Ethernet Switch Diagram                                                    | . 62 |

| Figure 31. | Far-end Loopback Block Diagram                                                             | . 64 |

| Figure 32. | Near-end Loopback Block Diagram                                                            | . 65 |

| Figure 33. | Connector Loopback Block Diagram                                                           |      |

| Figure 34. | EEPROM Interface Connections                                                               | . 73 |

| Figure 35. | PHY Startup and Initialization Sequence                                                    | . 75 |

| Figure 36. | Extended Page Register Diagram                                                             |      |

| Figure 37. | GMII Transmit AC Timing in 1000BASE-T Mode                                                 |      |

| Figure 38. | GMII Receive AC Timing in 1000BASE-T Mode                                                  |      |

| Figure 39. | MII Transmit AC Timing (100Mbps)                                                           |      |

| Figure 40. | MII Receive AC Timing (100Mbps)                                                            | 147  |

### VSC8211 Datasheet

| Figure 41. | TBI Transmit AC Timing                              | 148 |

|------------|-----------------------------------------------------|-----|

| Figure 42. | TBI Receive AC Timing                               | 149 |

| Figure 43. | RGMII/RTBI Uncompensated AC Timing and Multiplexing | 151 |

| Figure 44. | RGMII/RTBI Compensated AC Timing and Multiplexing   | 152 |

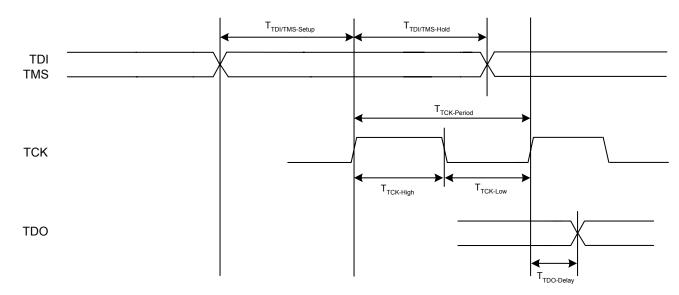

| Figure 45. | JTAG Interface AC Timing                            | 153 |

| Figure 46. | SMI AC Timing                                       | 154 |

| Figure 47. | LED_CLK and LED_DATA Output AC Timing               | 155 |

| Figure 48. | REFCLK AC Timing                                    | 156 |

| Figure 49. | CLKOUTMAC AC Timing                                 | 157 |

| Figure 50. | CLKOUTMICRO AC Timing                               | 157 |

| Figure 51. | RESET AC Timing                                     | 158 |

| Figure 52. | 117-ball 10x14mm LBGA Mechanical Specification      | 159 |

|            |                                                     |     |

# Tables

| Table 1.  | Signal Type Description                                          |     |  |

|-----------|------------------------------------------------------------------|-----|--|

| Table 2.  | Configuration and Control Signals                                |     |  |

| Table 3.  | System Clock Interface Signals (SCI)                             |     |  |

| Table 4.  | Analog Bias Signals                                              |     |  |

| Table 5.  | JTAG Access Port                                                 |     |  |

| Table 6.  | Serial Management Interface Signals                              | 24  |  |

| Table 7.  | EEPROM Interface Signals                                         |     |  |

| Table 8.  | LED Interface Signals                                            |     |  |

| Table 9.  | Parallel MAC Interface Signals - Transmit Signals                |     |  |

| Table 10. | Parallel MAC Interface Signals - Receive Signals                 |     |  |

| Table 11. | Serial MAC/Media Interface Signals                               |     |  |

| Table 12. | Twisted Pair Interface Signals                                   |     |  |

| Table 13. | Power Supply and Ground Connections                              |     |  |

| Table 14. | No Connects                                                      |     |  |

| Table 15. | Power Supply and Associated Functional Signals                   |     |  |

|           | Accepted MDI Pair Connection Combinations                        |     |  |

|           | SMI Pin Descriptions - MSA Mode                                  |     |  |

| Table 18. | SMI Pin Descriptions - MSA Mode                                  |     |  |

|           | SMI Frame Format                                                 |     |  |

|           | LED Function Assignments                                         |     |  |

|           | Parallel LED Functions                                           |     |  |

|           | LED Output Options                                               |     |  |

| Table 23. | JTAG Device Identification Register Description                  |     |  |

|           | JTAG Interface Instruction Codes                                 |     |  |

| Table 25. | CMODE Pull-up/Pull-down Resistor Values                          |     |  |

| Table 26. | CMODE Bit to PHY Operation Condition Parameter Mapping           |     |  |

|           | PHY Operating Condition Parameter Description                    |     |  |

|           | Configuration EEPROM Data Format                                 |     |  |

|           | PHY Operating Modes                                              |     |  |

|           | Clause 28 Register View Remote Fault Transmitted to Link Partner |     |  |

|           | Clause 37 Register View Remote Fault Transmitted to Link Partner |     |  |

|           | Clause 28 Autonegotiation Link Partner Remote Fault              |     |  |

|           | Clause 37 Autonegotiation Link Partner Remote Fault              |     |  |

|           | PHY Register Names and Addresses                                 |     |  |

|           | Bit Sequences for Generating Quinary Symbols                     |     |  |

|           | PHY Operating Modes                                              |     |  |

|           | Absolute Maximum Ratings                                         |     |  |

|           | Recommended Operating Conditions                                 |     |  |

|           | PCB and Environmental Conditions                                 |     |  |

| Table 40. | Thermal Resistance Data                                          | 135 |  |

### VSC8211 Datasheet

| Table 41. | Thermal Specifications - 117 ball LBGA 10x14mm package                                                 | 135        |

|-----------|--------------------------------------------------------------------------------------------------------|------------|

|           | VDDIO @ 3.3V, RGMII-CAT5, 1000BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, Mode off     | 136        |

| Table 43. | VDDIO @ 3.3V, RGMII-100BASE-FX, FDX, 1518 Byte Random data packet, 100% Utilization, SFP M Off         |            |

| Table 44. | VDDIO @ 2.5V, RGMII-CAT5, 1000BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, Mode off     |            |

|           | VDDIO @ 3.3 V, RGMII-CAT5, 100BASE-TX, FD, 1518 Byte Random data packet, 100% Utilization, Mode off    | 137        |

|           | VDDIO @ 2.5 V, RGMII-CAT5, 100BASE-TX, FD, 1518 Byte Random data packet, 100% Utilization, Mode off    | 137        |

|           | VDDIO @ 3.3 V, RGMII-CAT5, 10BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, S<br>Mode off | 138        |

| Table 48. | VDDIO @ 2.5 V, RGMII-CAT5, 10BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, S<br>Mode off |            |

|           | VDDIO @ 3.3 V, RGMII-Fiber, 1000BASE-X, FD, 1518 Byte Random data packet, 100% Utilization, Mode off   | 139        |

| Table 50. | VDDIO @ 2.5 V, RGMII-Fiber, 1000BASE-X, FD, 1518 Byte Random data packet, 100% Utilization, Mode off   |            |

| Table 51. | VDDIO @ 3.3 V, SerDes-CAT5, 1000BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, Mode off   |            |

| Table 52. | VDDIO @ 2.5 V, SerDes-CAT5, 1000BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, Mode off   | SFP<br>140 |

| Table 53. | VDDIO @ 3.3 V, SerDes-CAT5, 1000BASE-T, FD, 1518 Byte Random data packet, 100% Utilization, Mode on    |            |

| Table 54. | Digital Pins Specifications (VDDIO = 3.3 V)                                                            | 141        |

| Table 55. | Digital Pins Specifications (VDDIO = 2.5 V)                                                            | 141        |

| Table 56. | Current Sinking Capability of LED Pins                                                                 | 142        |

| Table 57. | Reference Clock Option Specifications                                                                  | 142        |

|           | Crystal Option Specifications                                                                          |            |

| Table 59. | SerDes Specifications                                                                                  | 144        |

|           | GMII Mode Transmit Timing (1000BASE-T) Specifications                                                  |            |

| Table 61. | GMII Mode Receive Timing (1000BASE-T) Specifications                                                   | 146        |

| Table 62. | MII Transmit AC Timing Specifications (100 Mbps)                                                       | 147        |

| Table 63. | MII Receive Timing Specifications (100 Mbps)                                                           | 147        |

| Table 64. | TBI Mode Transmit Timing                                                                               | 148        |

| Table 65. | TBI Mode Receive Timing                                                                                | 149        |

| Table 66. | RGMII/RTBI Mode Timing                                                                                 | 150        |

| Table 67. | JTAG Timing                                                                                            | 153        |

| Table 68. | SMI Timing                                                                                             | 154        |

| Table 69. | MDINT Timing                                                                                           | 155        |

| Table 70. | Serial LED_CLK and LED_DATA Timing                                                                     | 155        |

| Table 71. | REFCLK Timing                                                                                          | 156        |

|           | CLKOUTMAC and CLKOUTMICRO Timing                                                                       |            |

| Table 73. | RESET AC Timing Specification                                                                          | 158        |

| Table 74. | SerDes Jitter                                                                                          | 161        |

VMDS-10105 Revision 4.1 October 2006

## **5** Relevant Specifications & Documentation

The VSC8211 conforms to the following specifications. Please refer to these documents for additional information.

| Specification - Revision                                                  | Description                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE 802.3-2002                                                           | Carrier Sense Multiple Access with Collision Detection (CSMA/CD) Access Method and<br>Physical Layer Specifications. IEEE 802.3-2002 consolidates and supersedes the following<br>specifications:<br>802.3ab (1000BASE-T), 802.3z (1000BASE-X), 802.3u (Fast Ethernet), with references to<br>ANSI X3T12 TP-PMD standard (ANSI X3.263 TP-PMD). |

| IEEE 1149.1-1990                                                          | Test Access Port and Boundary Scan Architecture <sup>1</sup> .<br>Includes IEEE Standard 1149.1a-1993 and IEEE Standard 1149.1b-1994.                                                                                                                                                                                                          |

| JEDEC EIA/JESD8-5                                                         | 2.5V±0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuits.                                                                                                                                                                                             |

| JEDEC JESD22-A114-B                                                       | Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM).<br>Revision of JESD22-A114-A.                                                                                                                                                                                                                                        |

| JEDEC JESD22-A115-A                                                       | Electrostatic Discharge (ESD) Sensitivity Testing Machine Model (MM).<br>Revision of EIA/JESD22-A115.                                                                                                                                                                                                                                          |

| JEDEC EIA/JESD78                                                          | IC Latch-Up Test Standard.                                                                                                                                                                                                                                                                                                                     |

| MIL-STD-883E                                                              | Miltary Test Method Standard for Microcircuits.                                                                                                                                                                                                                                                                                                |

| Cisco SGMII v1.7                                                          | Cisco SGMII specification                                                                                                                                                                                                                                                                                                                      |

| RGMII Specification - v2.0                                                | Reduced Pin-Count Interface for Gigabit Ethernet Physical Layer Devices (per Hewlett Packard).<br>Includes both RGMII and RTBI standards.                                                                                                                                                                                                      |

| PICMG 2.16                                                                | IP Backplane for CompactPCI.                                                                                                                                                                                                                                                                                                                   |

| Advanced TCA™ Base<br>PICMG 3.0                                           | IP Backplane specification for CompactPCI v3.0.                                                                                                                                                                                                                                                                                                |

| Cisco InLine Power Detection<br>Algorithm                                 | Cisco Systems InLine Power Detection:<br>http://www.cisco.com/en/US/products/hw/phones/ps379/<br>products_tech_note09186a00801189b5.shtml                                                                                                                                                                                                      |

| Small Form-factor Pluggable<br>(SFP) Transceiver MultiSource<br>Agreement | Specification for pluggable fiber optic transceivers. Describes module data access protocol and interface.                                                                                                                                                                                                                                     |

<sup>1</sup> Often referred to as the "JTAG" test standard.

## 6 Datasheet Conventions

| Convention                                         | Syntax                                                | Examples            | Description                                                                                             |

|----------------------------------------------------|-------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|

| Register<br>number                                 | RegisterNumber.Bit<br>or<br>RegisterNumber.BitRange   | 23.10<br>23.12:10   | Register 23 (address 17h), bit 10.<br>Register 23 (address 17h), bits 12, 11, and 10.                   |

| Extended<br>Page Regis-<br>ter Number <sup>1</sup> | RegisterNumberE.Bit<br>or<br>RegisterNumberE.BitRange | 23E.10<br>23E.12:10 | Extended Register 23 (address 17h), bit 10.<br>Extended Register 23 (address 17h), bits 12, 11, and 10. |

| Signal name<br>(active high)                       | SIGNALNAME <sup>2</sup>                               | PLLMODE             | Signal name for PLLMODE.                                                                                |

| Signal name<br>(active low)                        | SIGNALNAME <sup>2</sup>                               | RESET               | Active low reset signal.                                                                                |

| Signal bus<br>name BUSNAME[MSB:LSB] <sup>2</sup>   |                                                       | RXD[4:2]            | Receive Data bus, bits 4, 3, and 2.                                                                     |

Conventions used throughout this datasheet are specified in the following table.

<sup>1</sup> For more information about MII Extended Page Registers, see Section 24: "PHY Register Set Conventions," page 80.

<sup>2</sup> All signal names are in all CAPITAL LETTERS.

# 7 Document History and Notices

| Revision<br>Number | Date         | Comments                                                                                                                                                                                                                                                                  |

|--------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1.0              | Feb. 13 04   | First Preliminary Release                                                                                                                                                                                                                                                 |

| 0.1.1              | May 11 04    | Updated pin description with VDD12A and Power supply recommendations.<br>Added Errata Section.<br>Updated 'specification' section with VDD12A reference.<br>Updated LED ECO changes.<br>Added GMII,MII,TBI timing sections                                                |

| 2.0                | July 08 04   | Updated document style to reflect Vitesse corporate standards.<br>Replaced Errata section with Design Guidelines section.                                                                                                                                                 |

| 4.0                | August 17 05 | Added lead-free (Pb-free) package information.<br>Updated register section.<br>Added Reset Timing section.                                                                                                                                                                |

|                    |              | <ul> <li>In the media converter application diagram, the RJ-45 speed was corrected from<br/>10/100/1000BASE-T to 1000BASE-T.</li> </ul>                                                                                                                                   |

|                    |              | <ul> <li>Throughout the datasheet, information was added regarding the 100BASE-FX<br/>mode. The following lists the main information:</li> </ul>                                                                                                                          |

|                    | October 2006 | <ul> <li>For information about twisted pair signals in 100BASE-FX mode, see Table 12:<br/>"Twisted Pair Interface Signals".</li> </ul>                                                                                                                                    |

|                    |              | <ul> <li>For information about 100BASE-FX system schematics, see Figure 13: "System<br/>Schematic – '100Mbps Fiber Media' Implementation".</li> </ul>                                                                                                                     |

|                    |              | <ul> <li>For information about 100BASE-FX connections and initialization, see Section<br/>11.5: "100Mbps Fiber Support Over Copper Media Interface" and Section 33.4:<br/>"100BASE-FX Initialization Script".</li> </ul>                                                  |

|                    |              | <ul> <li>For information about 100BASE-FX current consumption, see Table 43: "VDDIO<br/>@ 3.3V, RGMII-100BASE-FX, FDX, 1518 Byte Random data packet, 100%<br/>Utilization, SFP Mode Off".</li> </ul>                                                                      |

| 4.1                |              | <ul> <li>In the list of LED function assignments, the function of LED pin 3, value 00, was<br/>corrected from Collision to Link/Activity.</li> </ul>                                                                                                                      |

|                    |              | <ul> <li>In the listing of JTAG interface instruction codes, the register width given for the<br/>instructions EXTEST and SAMPLE/PRELOAD was corrected from 196 bits to 78<br/>bits.</li> </ul>                                                                           |

|                    |              | <ul> <li>The MII transmit timing diagram was redrawn to more accurately reflect the delay<br/>from TXCLK to TXD[3:0], TXEN, and TXER. For more information about this<br/>specification, see Figure 39: "MII Transmit AC Timing (100Mbps)".</li> </ul>                    |

|                    |              | • In the JTAG interface AC timing diagram, missing labels were added that had been left out in the prior revision.                                                                                                                                                        |

|                    |              | <ul> <li>In the reset AC timing diagram, the MDIO signal pulse width was widened to be<br/>more accurate relative to the pulse width of the REFCLK signal. For more<br/>information about this specification, see Figure 51: "RESET AC Timing".</li> </ul>                |

|                    |              | <ul> <li>In the reset AC timing specifications, T<sub>READY</sub> signal, a condition was added that if<br/>EEPROM is present, an additional 100ms is required. For more information about<br/>reset AC timing, see Table 73: "RESET AC Timing Specification".</li> </ul> |

# 8 Device Block Diagram

The diagram below depicts the primary functional blocks and pins for the VSC8211.

Figure 5. VSC8211 Block Diagram

## 9 Package Pin Assignments & Signal Descriptions

### 9.1 VSC8211 117-Ball LBGA Package Ball Diagram

The following diagram shows the view from the top of the package with underlying BGA ball positions superimposed.

1.0 mm Ball Pitch (10 mm x 14 mm body) (Top View)

|   | 1     | 2      | 3               | 4                | 5                      | 6                           | 7                | 8      | 9      | 10                         | 11     | 12     | 13     |   |

|---|-------|--------|-----------------|------------------|------------------------|-----------------------------|------------------|--------|--------|----------------------------|--------|--------|--------|---|

| A | TXEN  | GTXCLK | TXCLK           | RXER             | RXDV                   | RXD1                        | RXD3             | RXD5   | RXD7   | MODDEF0/<br>CLKOUT-<br>MAC | TDI    | RESET  | LED0   | А |

| в | TXD1  | TXDO   | TXER            | COL              | RXCLK                  | RXD0                        | RXD2             | RXD4   | RXD6   | TMS                        | TDO    | LED1   | LED2   | в |

| С | TXD3  | TXD2   | VDDIOMAC        | CRS              | VSS                    | VDDIOMAC                    | RXLOS/<br>SIGDET | TRST   | тск    | VDD12                      | VDD12  | LED3   | LED4   | С |

| D | TXD5  | TXD4   | VDDIOMAC        | VSS              | VSS                    | VSS                         | VSS              | VSS    | VSS    | VDDIOCTRL                  | CMODE7 | CMODE6 | CMODE5 | D |

| Е | TXD7  | TXD6   | NC              | VSS              | VSS                    | VSS                         | VSS              | VSS    | VSS    | VSS                        | CMODE2 | CMODE3 | CMODE4 | Е |

| F | SDON  | SDOP   | VDD12           | VDD12            | VSS                    | VSS                         | VSS              | VSS    | VSS    | VDD33A                     | CMODE0 | TXVND  | TXVPD  | F |

| G | SDIN  | SDIP   | VDD12           | MODDEF2/<br>MDIO | TXDIS/<br>SRESET       | CLKOUT-<br>MICRO/<br>OSCDIS | VDDIO-<br>MICRO  | VDD33A | VDD33A | VDD33A                     | CMODE1 | TXVNC  | TXVPC  | G |

| н | RDN   | RDP    | MODDEF1/<br>MDC | MDINT            | EEDAT                  | REFFILT                     | VDD12A           | NC     | VSS    | XTAL2                      | VSS    | TXVNB  | TXVPB  | н |

| J | SCLKP | SCLKN  | TDP             | TDN              | EECLK/<br>PLLM-<br>ODE | REFREXT                     | VSS              | NC     | VSS    | XTAL1/<br>REFCLK           | VSS    | TXVNA  | TXVPA  | J |

|   | 1     | 2      | 3               | 4                | 5                      | 6                           | 7                | 8      | 9      | 10                         | 11     | 12     | 13     |   |

9.2 LBGA Ball to Signal Name Cross Reference<sup>1</sup>

Figure 7. 117-Ball LBGA Signal Map (top view)

Downloaded by spatni@partminer.com on November 22, 2006 from Vitesse.com

<sup>&</sup>lt;sup>1</sup>GMII Signal Names are shown for all Parallel MAC Interface Signals, except TXCLK (A3). See Section 9.4.8 on page 26 and Section 9.4.9 on page 28 for Signal Names in other Parallel MAC Interface Modes.

## 9.3 Signal Type Description

| Table 1. | Signal Type  | e Description |

|----------|--------------|---------------|

|          | orginal type | Booonphon     |

| Symbol             | Signal Type                  | Description                                                                                                                                                                                                                                        |

|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                  | Digital Input                | Standard digital input signal. No internal pull-up or pull-down.                                                                                                                                                                                   |

| I <sub>PU</sub>    | Digital Input with Pull-up   | Standard digital input. Includes on-chip $100k\Omega$ pull-up to VDDIOMAC, VDDIOMI-<br>CRO, VDDIOCTRL, or the VDD33A supply. Refer to Section 9.5: "Power Supply<br>and Associated Functional Signals" for details.                                |

| I <sub>PU5V</sub>  | Digital Input with Pull-up   | Standard digital input. Includes on-chip $100k\Omega$ pull-up to VDDIOMAC, VDDIOMI-<br>CRO, VDDIOCTRL, or the VDD33A supply. Refer to Section 9.5: "Power Supply<br>and Associated Functional Signals" for details. This input pin is 5V tolerant. |

| I <sub>PD</sub>    | Digital Input with Pull-down | Standard digital input. Includes on-chip 100k $\Omega$ pull-down to GND.                                                                                                                                                                           |

| I <sub>PD5V</sub>  | Digital Input with Pull-down | Standard digital input. Includes on-chip 100k $\Omega$ pull-down to GND. This input pin is 5V tolerant.                                                                                                                                            |

| I <sub>DIFF</sub>  | Differential Input Pair      | SerDes differential input pair with $100\Omega$ or $150\Omega$ differential terminations. Pins should be AC-coupled with external $0.01\mu$ F capacitors.                                                                                          |

| 0                  | Digital Output               | Standard digital output signal.                                                                                                                                                                                                                    |

| O <sub>ZC</sub>    | Impedance Controlled Output  | $50\Omega$ integrated (on-chip) source series terminated, digital output signal. Used pri-<br>marily for timing-sensitive, high speed MAC I/F and 125MHz clock output pins, in<br>addition to high speed manufacturing test mode pins.             |

| O <sub>DIFF</sub>  | Differential Output Pair     | SerDes differential output pair, with on-chip $100\Omega$ or $150\Omega$ differential terminations.<br>Pins should be AC-coupled with external $0.01\mu$ F capacitors.                                                                             |

| I/O                | Digital Bidirectional        | Tristate-able, digital input and output signal.                                                                                                                                                                                                    |

| I <sub>PU</sub> /O | Digital Bidirectional        | Tristate-able, digital input and output signal. Includes on-chip 100kΩ pull-up to VDDIOMAC, VDDIOMICRO, VDDIOCTRL, or the VDD33A supply. Refer to Section 9.5: "Power Supply and Associated Functional Signals" for details.                       |

| I <sub>PD</sub> /O | Digital Bidirectional        | Tristate-able, digital input and output signal. Includes on-chip 100k $\Omega$ pull-down to GND.                                                                                                                                                   |

| OD                 | Digital Open Drain Output    | Open drain digital output signal. Must be pulled to VDDIOMICRO through an exter-<br>nal pull-up resistor.                                                                                                                                          |

| A <sub>DIFF</sub>  | Analog Differential          | Analog differential signal pair for twisted pair interface.                                                                                                                                                                                        |

| A <sub>BIAS</sub>  | Analog Bias                  | Analog bias or reference signal. Must be tied to external resistor and/or capacitor bias network, as shown in Section 10: "System Schematics".                                                                                                     |

| Ι <sub>Α</sub>     | Analog Input                 | Analog input for sensing variable voltage levels.                                                                                                                                                                                                  |

| OS                 | Open Source                  | Open source digital output signal. Must be pulled to GND through an external pull-<br>down resistor.                                                                                                                                               |

| Р                  | Power Supply                 | Power supply connection. Must be connected to specified power supply plane.                                                                                                                                                                        |

| G                  | GND                          | Ground Connection. Must be connected to ground.                                                                                                                                                                                                    |

| NC                 | No Connect                   | No connect signal. Must be left floating.                                                                                                                                                                                                          |

VMDS-10105 Revision 4.1 October 2006

#### 9.4 Detailed Pin Descriptions

#### 9.4.1 Configuration and Control Signals

#### Table 2. Configuration and Control Signals

| 117 LBGA<br>Ball                                     | Signal Name                                                                  | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------|------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D11<br>D12<br>D13<br>E13<br>E12<br>E11<br>G11<br>F11 | CMODE7<br>CMODE6<br>CMODE5<br>CMODE4<br>CMODE3<br>CMODE2<br>CMODE1<br>CMODE0 | I <sub>A</sub>  | Hardware Chip Mode Select.<br>The CMODE inputs are used for hardware configuration of the various operating<br>modes of the PHY. Each pin has multiple settings, each of which is established by<br>an external 1% resistor tied to GND or VDD33A. See Section 19: "Hardware Con-<br>figuration Using CMODE Pins" for details on configuring the PHY with the CMODE<br>pins.                                                                                                                                                                                                                                                                                                                                    |

| A12                                                  | RESET                                                                        | I               | Hardware Chip Reset.<br>RESET is an active low input. When asserted, it powers down all of the internal ref-<br>erence voltages and the PLLs. It resets all internal logic, including the DSPs and the<br>MII Management Registers.<br>Hardware reset is distinct from soft reset which only resets the port to accept new<br>configuration based on register settings.                                                                                                                                                                                                                                                                                                                                         |

| G5                                                   | TXDIS/<br>SRESET                                                             | Ι <sub>ΡU</sub> | Transmit Disable or Software Reset.When asserted, it places the PHY in a low power state, which includes disabling the<br>SerDes interface. Although the device is powered down, non-volatile, Serial Man-<br>agement Interface registers retain their values.TXDIS and SRESET are simply two names for the same function. The assertion<br>state (active high or low respectively) of this input pin is determined by the value of<br>Extended MII Register 21E.15 'SFP MODE' set at startup using Hardware Configu-<br>ration or via the EEPROM interface. Refer to Section 19: "Hardware Configuration<br>Using CMODE Pins" and Section 20: "EEPROM Interface" for details on configura-<br>tion at startup. |

#### 9.4.2 System Clock Interface Signals (SCI)

| Table 3. | System Clock  | Interface | Signals     | (SCI) |

|----------|---------------|-----------|-------------|-------|

|          | Oystern Olock | micriace  | Orginalis ( |       |

| 117 LBGA<br>BALL | Signal Name            | Туре               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|