## datasheet

IP

### Xilinx Virtex<sup>™</sup>-II Development Kit

The Virtex-II Development Kit provides a complete

hardware environment for designers to accelerate their

time to market. The kit delivers a stable platform to

develop and test designs targeted to the highly

advanced Xilinx Virtex-II FPGA family. The installed

FPGA device offers up to a 6 Million system gate

prototyping environment to effectively demonstrate the

enhanced benefits of the leading edge Xilinx FPGA

solution. Embedded multipliers, advanced digital clock

immersion, and other exciting features can be

implemented with advanced Xilinx design tools.

Demonstration VHDL code is included with the kit to

exercise standard peripherals on the evaluation board

The Virtex-II Development Board is shipped with

functionality of the board. All source code for these

demonstrations will be included in the kit with the

Refer to the table at the end of this document or see it

on the Internet at http://www.ads.avnet.com/.

demonstration/test code to show basic

for a quick start to device familiarization.

**Demo Application**

exception of licensed IP.

**Ordering Information**

basic

management, built-in impedance matching,

Description

#### Features

- Large Xilinx Virtex-II FPGA

- XC2V1500-FF896- 1.5 Million System Gates

- XC2V4000-FF1152- 4 Million System Gates

- XC2V6000-FF1152- 6 Million System Gates

- Configuration

- JTAG Connectors Support Multilynx, Parallel III & Parallel IV JTAG cables

- Xilinx XCCACEMxx-BG388I System ACE MPM Solution

- Memory

- 133 MHz, 128 MB DDR SDRAM DIMM

- 8 MB FLASH (onboard)

- 64 MB SDRAM <sup>(1)</sup>

- 16 MB FLASH (1)

- 1 MB SRAM (1)

- PCI/PCI-X interface

- Universal connector 3.3V/5V, 32/64-bit

- Communication

- RS232 Serial Port (DB9)

- 10/100/1000 Ethernet<sup>(1)</sup>

- USB 2.0 <sup>(1)</sup>

- IRDA (1)

- PS2 Keyboard/mouse<sup>(1)</sup>

- Expansion Connectors

- 140-pin I/O expansion connectors (AvBus)

- Six on 2V4000 & 6000 boards

- Four on 2V1500 boards

- Pin Headers for simple low pin count connections

- Support for Versatile I/O & LVDS

- Miscellaneous

- 8 DIP switches

- 2 Push-buttons

- 8 LEDs

- 40MHz, 50MHz, and 125MHz oscillators

- Power

- +5.0 VDC Power Connector (supply included)

- +3.3 VDC Regulated

- +2.5 VDC Regulated

- +1.8 VDC Regulated

- +1.5 VDC Regulated

- (1) These features are only available with

the ADS Communications/Memory Module installed

#

Copyright © 2002 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. AVNET AVENUE and AVNET AVENUE & Design are trademarks of Avnet, Inc. All other trademarks are property of their respective owners.

#### FPGA

The Virtex-II Development Board can be ordered with FPGAs of varying sizes depending on the customer's needs. The options are: XC2V1500-5FF896 (528 total I/O and ~1.5M Logic Gates), XC2V4000-4FF1152 or XC2V6000-4FF1152C (824 total I/O and ~4M and 6M Logic Gates).

#### **FPGA** Configuration

Configuration of the on board Virtex-II FPGA can be accomplished via JTAG or for the installed System ACE Multi-Package Module (MPM). This module can hold up to 8 jumper selectable configurations allowing the user to quickly change between configurations without the use of a host computer. A battery holder is provided to enable the bit stream protection feature of the Virtex-II device.

#### **JTAG Chain**

The Virtex-II development board has two (2) devices in its JTAG chain, the FPGA and the System ACE MPM. The JTAG Header provides connections for both the JTAG and SelectMap programming of the FPGA and System ACE MPM. A second JTAG header (2mm) is provided to support the ribbon cable connection used with the Xilinx Parallel IV cable.

#### Memory

Memory is provided on this board to enable advanced user applications including communication switches and high end Microprocessor or DSP IP Cores.

#### **DDR SDRAM**

The DDR SDRAM interface is implemented in the form of a single 200 pin SO-DIMM socket providing a 64bit wide data path. The included module is 128 MB but the design supports up to 512 MB modules for user expansion. The board was designed to support memory clock rates up to 133 MHz (266 Mb/sec/pin).

#### FLASH

The FLASH memory consists of one 8 MB device in a 16-bit configuration (64Mb). The FLASH shares bus and control signals with an AvBus connector.

#### **Extended Memory**

64 MB SDRAM, 16 MB FLASH, and 1 MB SRAM can be added by installing the ADS Communications/Memory Module on to 2 AvBus connectors. Additional expansion can be realized via custom daughter cards.

#### PCI/PCI-X

The Virtex-II Development board has been constructed in the form of a universal (+3.3V/+5V, 32/64-Bit, 33/66/100MHz) PCI expansion card\*. When installed in a slot the board can be powered from the Backplane. Functionality of this interface requires the creation or purchase of an IP core to provide the signaling.

\*The card is designed fit and function in a PCI/PCI-X Motherboard or Backplane but it is not compatible with the standard.

#### Communication

An RS232 serial port is provided on the board to allow terminal based user I/O. Expanded communication functions: 10/100/1000 Ethernet, USB 2.0, IRDA, and PS2 Keyboard/mouse can be demonstrated on the board by installing the ADS Communications Memory Module on the AvBus expansion connectors.

#### **Expansion Capabilities**

All of the I/O pins of the installed FPGA that are not dedicated to on board functions are made available through the installed connectors for user I/O. Most of these signals are point-to-point connections between the FPGA and a single connector pin but some have more then one use. Consult the User Manual or schematic for a detailed description.

#### **AvBus Connectors**

High pin count board-to-board connectors with common pinouts (AvBus) provide maximum flexibility for the user. It is comprised of a 2:1 signal to power/ground ratio, implemented to ensure signal integrity, and controlled impedance continuity. The connectors realize an effective I/O count of 241 signals with the X2V1500 part or 541 signals with the X2V4000 or XC2V6000.

These connectors can be used to interface with ADS Avalon daughter cards or the user's custom card.

#### Versatile and LVDS I/O

The Virtex-II Device supports several I/O signaling standards including LVDS. The ADS Virtex-II Development board can support all of the signal-ended standards on as many as 176 pins and differential standards on up to 38 LVDS Pairs.

#### I/O Signal Headers

Standard .100x.100 headers are provided to allow easy access for up to 106 I/O signals.

Copyright © 2002 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. AVNET AVENUE and AVNET AVENUE & Design are trademarks of Avnet, Inc. All other trademarks are property of their respective owners.

#### Miscellaneous

The "Miscellaneous" interfaces on the Virtex-II Dev board consist of a single 8-position DIP switch (8individual SPST switches), 8 LEDs and two pushbutton switches all connected directly to the FPGA.

#### **Clock Resources**

There are 4 clock sources provided for on the board: 66.6MHz and 125MHz Oscillators are soldered to the board, a socket is provided (40MHz Osc Installed) to allow easy user frequency selection and an SMA connector (Not Populated) is available to allow for an external clock source. All are connected to a Global Clock Inputs of the FPGA.

#### Power

The Virtex-II Development Board is powered via the +5.0 volt rail of the PCI connector or by an external +5V regulated to +/- 5% power supply. Voltages other then 5V are generated on board using appropriate regulators. 1.5V and 3.3V are provided at a maximum of 6A or 14A, depending on the power supply option ordered by switching regulators. Linear regulators are used for the remaining voltages including: 2.5V, 1.8V and 1.25V. I/O reference voltages not available from a regulator are created with resistor divider networks.

Note: Power requirements for the board are application specific; therefore it is the responsibility of the user to verify that ample power is supplied.

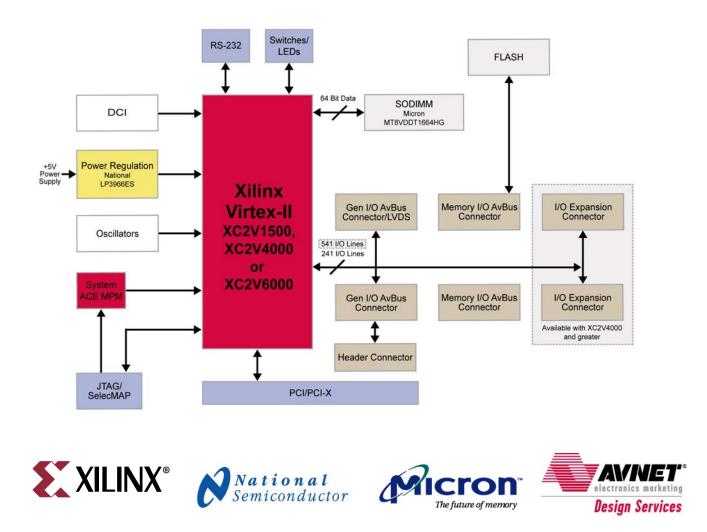

**Block Diagram**

Copyright © 2002 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. AVNET AVENUE and AVNET AVENUE & Design are trademarks of Avnet, Inc. All other trademarks are property of their respective owners.

| Part Number              | Hardware                                                                                                                                     |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| ADS-XLX-V2-DEV1500       | Xilinx Virtex-II Development Kit<br>populated with an XC2V1500 device                                                                        |

| ADS-XLX-MB-DEV1500       | Xilinx Virtex-II Development Kit<br>bundled with<br>Communications/Memory Module<br>and MicroBlaze Core License                              |

| ADS-XLX-V2-DEV4000       | Xilinx Virtex-II Development Kit<br>populated with an XC2V4000 device                                                                        |

| ADS-XLX-MB-DEV4000       | Xilinx Virtex-II Development Kit<br>bundled with<br>Communications/Memory Module<br>and MicroBlaze Core License                              |

| ADS-XLX-V2-<br>DEV4000XP | Xilinx Virtex-II Development Kit<br>populated with an XC2V4000 device<br>& high-current power supply                                         |

| ADS-V2-MB-DEV4000XP      | Xilinx Virtex-II Development Kit<br>bundled with<br>Communications/Memory Module,<br>MicroBlaze Core License & high-<br>current power supply |

| ADS-XLX-V2-<br>DEV6000XP | Xilinx Virtex-II Development Kit<br>populated with an XC2V6000 device<br>& high-current power supply                                         |

| ADS-V2-MB-DEV6000XP      | Xilinx Virtex-II Development Kit<br>bundled with<br>Communications/Memory Module,<br>MicroBlaze Core License & high-<br>current power supply |

Copyright © 2002 Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. AVNET AVENUE and AVNET AVENUE & Design are trademarks of Avnet, Inc. All other trademarks are property of their respective owners.