## AMBE-4020<sup>™</sup> Half-Duplex and AMBE-4020<sup>™</sup> Full-Duplex Vocoder Chips

User's Manual Version 2.6 October, 2021 AMBE-4020<sup>™</sup> Vocoder Chip Users Manual Version 2.6 October, 2021

(The most up to date version of the manual is always available at www.dvsinc.com)

© Copyright, 2015 Digital Voice Systems, Inc. 600 Cleveland Street STE 795 Clearwater, FL 33755

This document may not, in whole or in part be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior consent in writing from Digital Voice Systems, Incorporated. Every effort has been made to ensure the accuracy of this manual. However, Digital Voice Systems, Inc. makes no warranties with respect to the documentation and disclaims any implied warranties of merchantability and fitness for a particular purpose. Digital Voice Systems, Inc. shall not be liable for any errors or for incidental or consequential damages in connection with the furnishing, performance, or use of this manual or the examples herein. This includes business interruption and/or other loss which may arise from the use of this product. The information in this document is subject to change without notice.

Trademarks

AMBE-4020<sup>TM</sup> Vocoder Chip is a trademark of Digital Voice Systems, Inc. Other product names mentioned may be trademarks or registered trademarks of their respective companies and are the sole property of their respective manufacturers. All Rights Reserved Data subject to change

### Digital Voice Systems, Inc. END USER PRODUCT License Agreement

This non-exclusive END USER PRODUCT License Agreement (EUPLA) is a legal agreement between the customer of this PRODUCT (the END USER) and Digital Voice Systems, Inc. (DVSI) covering the terms and conditions under which this DVSI PRODUCT and DVSI's proprietary content (that may consist of and is not limited to software, hardware, documentation and other material) is licensed to the END USER.

#### 1. Preliminary Statements and Definitions

1.1 By installing, or otherwise using this PRODUCT the END USER agrees to be bound by the terms and conditions set forth in this EUPLA. If the END USER does not agree to the terms and conditions set forth in this EUPLA, then the END USER must not install or use the PRODUCT and shall immediately return the PRODUCT to DVSI as set forth in Section 13.

a) The PRODUCT shall mean the Hardware, Software, Documentation and other materials that were provided by DVSI, either directly or indirectly through distributors or third parties, to the END USER as part of a sale, delivery or other transaction.

b) Hardware can be in the form of Integrated Circuits (such as Digital signal Processors), Circuit boards and electronics enclosed in a chassis. DVSI's Vocoder Chips (AMBE-3000<sup>TM</sup>, AMBE-4020<sup>TM</sup>, etc...) are an example of an Integrated Circuit.

c) Software can be in form of computer code, firmware masked into an IC or stored or embedded into ROM or RAM or Flash memory, or software stored on any media (such as CD-ROM, floppy disk, hard drive, solid-state memory or the Internet)

d) Documentation means written or electronic information, including user manuals, technical documents, training materials, specifications or diagrams, that pertain to or are delivered with the PRODUCT in any manner (including in print, on CD-ROM, or on-line).

1.2 DVSI has developed a number of voice coding methods and algorithms (the "Technology") which include DVSI's Advanced Multi-Band Excitation ("AMBE®"), AMBE+TM, and AMBE+2TM voice coders. The Technology codes speech at low bit rates and may include error correction, echo cancellation and other auxiliary functions.

1.3 "DVSI Voice Compression Software" shall mean the voice coding Software that implements or embodies the Technology and is embedded into or otherwise provided with the PRODUCT.

1.4 "DVSI Voice Codec" shall mean the DVSI Voice Compression Software, any PRODUCT Hardware into which the DVSI Voice Compression Software is embedded or executed and any associated Documentation.

1.5 DVSI represents that it owns certain "Proprietary Rights" in the PRODUCT including patent rights, copyrights, trademarks and trade secrets. These rights include one or more of the following US Patents #6,912,495; #7,970,606; #8,036,886; #8,200,497, #8,315,860; #8,359,197; #8,433,562; and #8,595,002; and under other US and foreign patents, related patents and patents pending. AMBE®, AMBE+™ and AMBE+2™ are registered trademarks and trademarks of Digital Voice Systems, Inc.

1.6 "END USER" shall mean the person and/or organization to whom the DVSI Vocoder Product (software or hardware) was delivered or provided to as specified in the purchase order or other documentation. In the event that the END USER transfers his rights under this license to a third party as specified in Section 3.0, then this third party shall become an "END USER".

1.7 DVSI reserves the right to make modifications and other changes to its products and services at any time and to discontinue any product or service without notice.

#### 2. License Granted

2.1 Subject to the conditions herein and upon initial use of the DVSI Product, DVSI hereby grants to END USER a non-exclusive, limited license to use the DVSI Voice Compression Software and Technology solely as included by DVSI within the PRODUCT. No license, either expressed or implied, is granted for any use of the DVSI's Proprietary Rights on any other device or Hardware or in any manner other than within the original unmodified PRODUCT purchased from DVSI. No license is granted to copy or modify the DVSI Voice Compression Software or the PRODUCT either in whole or in part.

2.2 No license, right or interest in any trademark, trade name or service mark of DVSI is granted under this Agreement. END USER acknowledges that the PRODUCT may contain trade secrets of DVSI, including but not limited to the specific design, and associated interface information.

2.3 END USER shall not copy, extract, reverse engineer, disassemble, decompile or otherwise reduce the DVSI Voice Compression Software to human-readable form. END USER shall not alter, duplicate, make copies of, create derivative works from, distribute, disclose, provide or otherwise make available to others, the DVSI Voice Compression Software and Technology and/or trade secrets contained within the PRODUCT in any form to any third party without the prior written consent of DVSI. The END USER shall implement reasonable security measures to protect such trade secrets.

2.4 This is a license, not a transfer of title, to the DVSI Voice Compression Software, Technology and Documentation, and DVSI retains ownership and title to all copies.

#### 3. Transfer of License

3.1 The END USER shall have the right to transfer the rights under this EUPLA to a third party by providing the third party with a copy of this EUPLA and obtaining the third parties agreement to all the terms and conditions under this EUPLA. In the event END USER does transfer their rights to a third party in accordance with this EUPLA, then the third party transferee shall become the new END USER and all rights under this EUPLA shall terminate with respect to the transferor in accordance with Section 4.

#### 4. Term and Termination

4.1 This Agreement is effective upon initial delivery of the PRODUCT and shall remain in effect until terminated in accordance with this agreement.

4.2 This Agreement shall terminate automatically without notice from DVSI if END USER fails to comply with any of the material terms and conditions herein. END USER may terminate this Agreement at any time upon written notice to DVSI certifying that END USER has complied with the provisions of Section 13.

4.3 Upon termination of this Agreement for any reason, END USER shall: (a) discontinue all use of the PRODUCT; (b) return the PRODUCT and documentation purchased or acquired, or in Licensee's possession, to DVSI; (c) have no further rights to any DVSI Software or the Technology without a separate written license from DVSI; All confidentiality obligations of Customer and all limitations of liability and disclaimers and restrictions of warranty shall survive termination of this Agreement. In addition, the provisions of the sections titled "U.S. Government End User Purchasers" and "General Terms Applicable to the Limited Warranty Statement and End User License" shall survive termination of this Agreement.

#### 5. Payments

5.1 In consideration of the materials delivered as part of the PRODUCT, and in consideration of the license granted by DVSI for the PRODUCT, and in consideration of DVSI's performance of its obligations hereunder, the END USER agrees to pay to DVSI the fees as specified in DVSI's invoice. Payments of fees shall be received by DVSI prior to shipment of the PRODUCT.

#### 6. Proprietary Notices

6.1 END USER shall maintain and not remove or alter any copyright or proprietary notice on or in the PRODUCT.

6.2 Reproduction of non-proprietary information found in DVSI Users Manuals or data sheets is permissible only if the END USER reproduces without alteration, and includes all copyright and other proprietary notices, all associated warranties, conditions and limitations on all copies, in any form.

#### 7. Proprietary Information

7.1 The parties agree that the PRODUCT shall be considered Proprietary Information.

7.2 Except as otherwise provided in this Agreement, END USER shall not use, disclose, make, or have made any copies of the Proprietary Information, in whole or in part, without the prior written consent of DVSI.

#### 8. Limited Warranty

8.1 DVSI warrants the PRODUCT to be free from defects in materials and workmanship under normal use for a period of ninety (90) days from the date of delivery. The date of delivery is set forth on the packaging material in which the Product is shipped. This limited warranty extends only to the Customer who is the original purchaser. If the PRODUCT is found to be defective and the condition is reported to DVSI, within the warranty period, DVSI may, at its option, repair, replace, or refund of the purchase price of the PRODUCT. DVSI may require return of the PRODUCT as a condition to the remedy.

<u>Restrictions</u>. This warranty does not apply if the PRODUCT (a) has been altered, (b) has not been installed, operated, repaired, or maintained in accordance with instructions supplied by DVSI, (c) has been subjected to abnormal physical or electrical stress, misuse, negligence, or accident;

8.2 Except as stated in Section 8.1, the PRODUCT is provided "as is" without warranty of any kind. DVSI does not warrant, guarantee or make any representations regarding the use, or the results of the use, of the PRODUCT with respect to its correctness, accuracy, reliability, speech quality or otherwise. The entire risk as to the results and performance of the PRODUCT is assumed by the END USER. After expiration of the warranty period, END USER, and not DVSI or its employees, assumes the entire cost of any servicing, repair, replacement, or correction of the PRODUCT.

8.3 DVSI represents that, to the best of its knowledge, it has the right to enter into this Agreement and to grant a license to use the PRODUCT to END USER.

8.4 Except as specifically set forth in this Section 8, DVSI makes no express or implied warranties including, without limitation, the warranties of merchantability or fitness for a particular purpose or arising from a course of dealing, usage or trade practice, with respect to the PRODUCT. Some states do not allow the exclusion of implied warranties, so the above exclusion may not apply to END USER. No oral or written information or advice given by DVSI or its employees shall create a warranty or in any way increase the scope of this warranty and END USER may not rely on any such information or advice. The limited warranties under this Section 8 give END USER specific legal rights, and END USER may have other rights which vary from state to state.

#### 9. Limitation of Liability

9.1 The END USER agrees that the limitations of liability and disclaimers set forth herein will apply regardless of whether the END USER has accepted the product or service delivered by DVSI.

9.2 In no event shall DVSI be liable for any special, incidental, indirect or consequential damages resulting from the use or performance of the PRODUCT whether based on an action in contract, or for applications assistance, or product support, or tort (including negligence) or otherwise (including, without limitation, damages for loss of business revenue, profits, business interruption, and loss of business information or lost or damaged data), even if DVSI or any DVSI representative has been advised of the possibility of such damages.

9.3 Because some states or jurisdictions do not allow the exclusion or limitation of liability for consequential or incidental damages, the above limitations may not apply to END USER.

9.4 DVSI's maximum liability for damages arising under this Agreement shall be limited to 20% (twenty percent) of the fees paid by END USER for the particular PRODUCT that gave rise to the claim or that is the subject matter of, or is directly related to, the cause of action.

#### 10. Taxes

10.1 All payments required under Section 5 or otherwise under this Agreement are exclusive of taxes and END USER agrees to bear and be responsible for the payment of all such taxes (except for taxes based upon DVSI's income) including, but not limited to, all sales, use, rental receipt, personal property or other taxes which may be levied or assessed in connection with this Agreement.

#### 11. Export

11.1 DVSI represents that to the best of its knowledge, this PRODUCT has been shipped from the United States in accordance with the US Export Administration Regulations (EAR). The Purchaser, Distributor, or END USER hereby gives its assurance to DVSI that it will comply with all export and re-export restrictions and regulations of all United States government agencies and authorities as well as when applicable, European Union and other export agencies. Export regulations include and are not limited to restrictions, prohibiting export or re-export of this DVSI PRODUCT (a) into an USembargoed country or (b) to anyone person or entity named on any of the screening lists of the US Departments of Commerce, State and the Treasury. For a list of parties for which the US Government maintains restrictions on exports, re-exports or transfers of items, reference the Consolidated Screening List (CSL) which may be found at: (https://www.export.gov/article?id= Consolidated-Screening-List). The Purchaser, Distributor, or END USER represents and warrants that they are not located in any such country or named on any such list.

11.2 DVSI takes no responsibility, and will not refund any monies paid, for any shipment that gets delayed, held or seized by US export authorities due to non-compliance with any export law, restriction or regulation. Any Purchaser, Distributor, or END USER of this PRODUCT who is not familiar with US export law should seek professional advice to ensure that they are in full compliance.

11.3 DVSI makes no representation that an export or re-export license is or is not required, and if a license is required, that it will or will not be issued by the U.S. Department of Commerce. The Purchaser, Distributor, or END USER is solely responsible, at their own expense, for obtaining any US or other government permits, licenses or approvals required for the importing and/or exporting the PRODUCT. For up-to-date information regarding United States import / export laws and regulations please visit https://www.export.gov/.

#### 12. Governing Law

12.1 This Agreement is made under and shall be governed by and construed in accordance with the laws of the Commonwealth of Massachusetts, (USA), except that body of law governing conflicts of law. If any provision of this Agreement shall be held unenforceable by a court of competent jurisdiction, that provision shall be enforced to the maximum extent permissible, and the remaining provisions of this Agreement shall remain in full force and effect. This Agreement has been written in the English language, and the parties agree that the English version will govern.

#### 13.0 Notices

13.1 Any notices to DVSI which may be given hereunder shall be sent in writing to: Digital Voice Systems Inc., 600 Cleveland Street STE 795 Clearwater, FL 33755 USA

## **Table of Contents**

| 1 | PR                | ODUCT INTRODUCTION                                                                                                                                                                                                                                                                       | 1  |

|---|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1               | Advances in Vocoder Design                                                                                                                                                                                                                                                               | 1  |

|   | 1.2               | AMBE-4020™ Vocoder Chip Performance                                                                                                                                                                                                                                                      | 2  |

|   | 1.3               | Design Flexibility/Low Cost Integration                                                                                                                                                                                                                                                  | 2  |

|   | 1.4               | Proven Technology                                                                                                                                                                                                                                                                        | 2  |

| 2 | HA                | RDWARE INFORMATION                                                                                                                                                                                                                                                                       | 3  |

|   | 2.1               | AMBE-4020™ and AMBE-4020™ Full-Duplex Vocoder Chip Markings                                                                                                                                                                                                                              | 3  |

|   | 2.2               | AMBE-4020™ BGA Packaging labeling                                                                                                                                                                                                                                                        | 4  |

|   | 2.3               | LQFP Pin Assignments                                                                                                                                                                                                                                                                     | 5  |

|   | 2.4               | BGA Pin Assignments (Special Order Only)                                                                                                                                                                                                                                                 | 6  |

|   | 2.5               | Pin Out Table                                                                                                                                                                                                                                                                            | 7  |

|   | 2.6               | UART Interface                                                                                                                                                                                                                                                                           | 10 |

|   | 2.7               | Internal 16-bit ADC Interface                                                                                                                                                                                                                                                            | 12 |

|   | 2.8               | Internal 12-bit DAC Interface                                                                                                                                                                                                                                                            | 13 |

|   | 2.9               | Digital Mic Interface                                                                                                                                                                                                                                                                    | 13 |

|   | 2.<br>2.<br>2.    | ENC/DEC Push-to-Talk Duplex Control Pins10.1Starting the Encoder or Decoder via the ENC/DEC pins10.2Stopping the Encoder or Decoder via the ENC/DEC pins10.3Using ENC pin to switch between encoder and decoder with DEC pin held high10.4Treatment for Startup Overlapped with Shutdown |    |

|   | 2.11              | I2S Interface                                                                                                                                                                                                                                                                            | 16 |

|   | 2.12              | I2C Interface                                                                                                                                                                                                                                                                            | 19 |

|   | 2.13              | Boot Configuration Pins                                                                                                                                                                                                                                                                  | 20 |

|   | 2.14              | GPIO Pins                                                                                                                                                                                                                                                                                | 22 |

|   | 2.                | Crystal / Oscillator Usage<br>15.1 Input Clock Requirements<br>15.2 External Clock Source                                                                                                                                                                                                |    |

|   | 2.16              | OFRAME/IFRAME/UFRAME/GFRAME Framing Signals                                                                                                                                                                                                                                              | 24 |

| 3 | NC                | RMAL OPERATING CONDITIONS                                                                                                                                                                                                                                                                | 28 |

|   | 3.1               | Moisture handling ratings                                                                                                                                                                                                                                                                | 28 |

|   | 3.2               | ESD handling ratings                                                                                                                                                                                                                                                                     | 28 |

|   | 3.3               | Pin Capacitance Attributes                                                                                                                                                                                                                                                               | 28 |

|   | 3.4               | Thermal handling ratings                                                                                                                                                                                                                                                                 | 29 |

|   |                   | <ul> <li>4.1 Thermal Operating Requirements</li></ul>                                                                                                                                                                                                                                    |    |

|   | 3.5<br><i>3</i> . | Recommended Voltage and Current Operating Conditions                                                                                                                                                                                                                                     |    |

|   |                   | AC electrical characteristics                                                             |    |

|---|-------------------|-------------------------------------------------------------------------------------------|----|

|   |                   | 6.2 Voltage and Current Operating Behaviors                                               |    |

|   | 3.7               | 0                                                                                         |    |

|   | 3.8               | Wake Timing                                                                               |    |

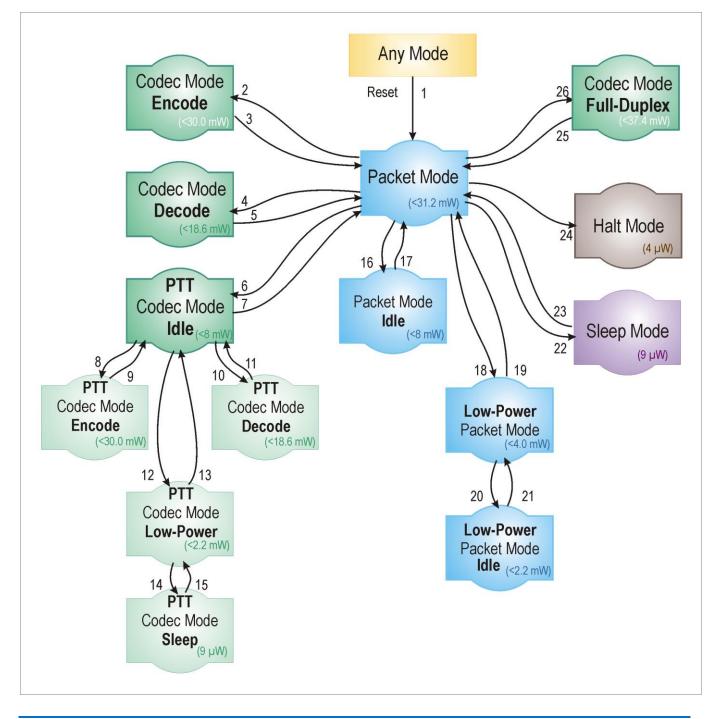

|   | 3.9               | Power Mode States and Transitions                                                         | 33 |

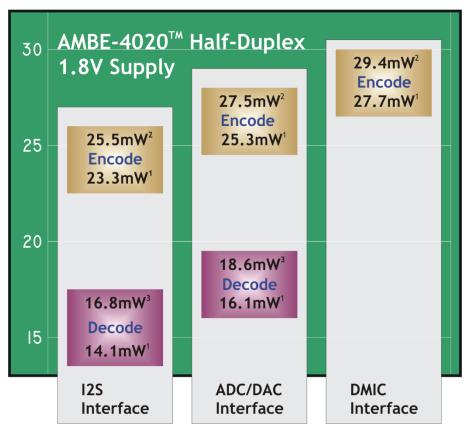

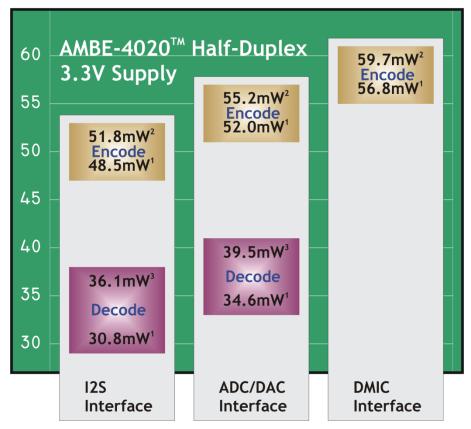

|   | 3.10              | Codec Mode Power Consumption                                                              | 36 |

|   | 3.11              | Packet Mode Power Consumption                                                             | 43 |

| 4 | INI               | TIAL DESIGN CONSIDERATIONS                                                                | 45 |

|   | 4.1<br><i>4</i> . | Vocoder Speech and FEC Rate Selection                                                     |    |

|   | 4.2               | Codec Interface Selection                                                                 | 48 |

|   | 4.3               | External A/D D/A selection                                                                |    |

|   | 4.4               | Vocoder Features                                                                          | 49 |

|   | 4.5               | Voice Activity Detection & Comfort Noise Insertion                                        |    |

|   | 4.6               | DTMF Dual Tone Multiple Frequency, Detection and Generation                               |    |

|   | 4.7               | Soft Decision Error Correction                                                            |    |

|   | 4.8               | Skew Control                                                                              |    |

|   | 4.9               | Noise Suppressor                                                                          |    |

|   | 4.9               | Echo Canceller                                                                            |    |

|   |                   |                                                                                           |    |

|   | 4.11              | Echo Suppressor                                                                           |    |

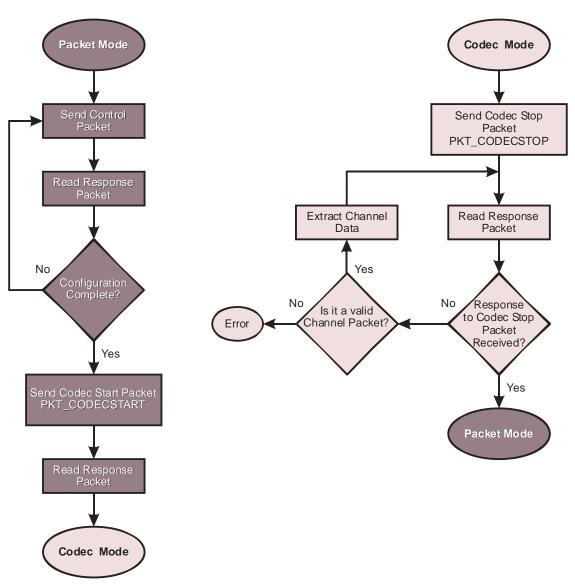

| 5 | OP                | ERATING MODES                                                                             | 53 |

|   | 5.1               | Packet Mode                                                                               |    |

|   |                   | 1.1 Flow Control in Packet Mode                                                           |    |

|   |                   | <ul> <li>1.2 Skew Control in Packet Mode</li> <li>1.3 Packet Mode - Idle</li> </ul>       |    |

|   |                   | 1.3         Packet Mode - Idle           1.4         Low Power Packet Mode                |    |

|   |                   | 1.5 Low Power Packet Mode - Idle                                                          |    |

|   |                   | 1.6 Sleep Mode                                                                            |    |

|   | 5.                | 1.7 Halt Mode                                                                             |    |

|   | 5.2               | Codec Mode                                                                                | 56 |

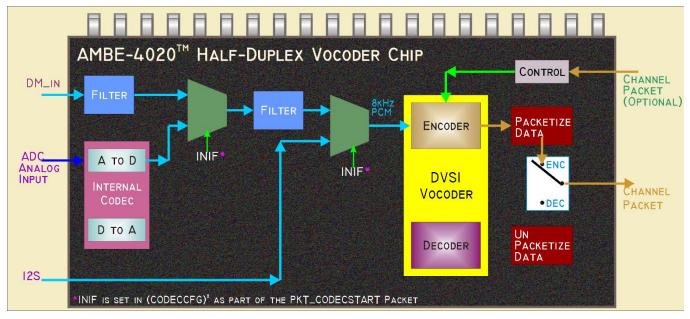

|   | 5.                | 2.1 Encoder Codec Mode                                                                    |    |

|   |                   | 2.2 Encoder Codec Passthru Mode                                                           |    |

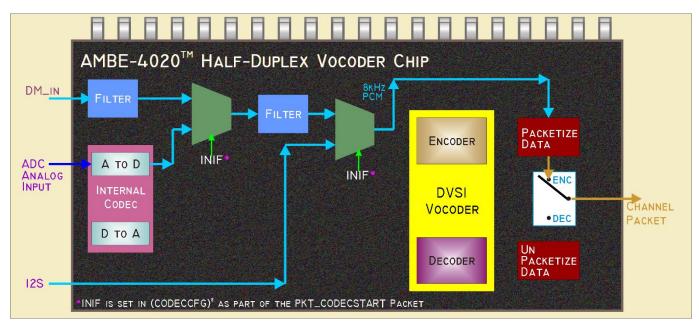

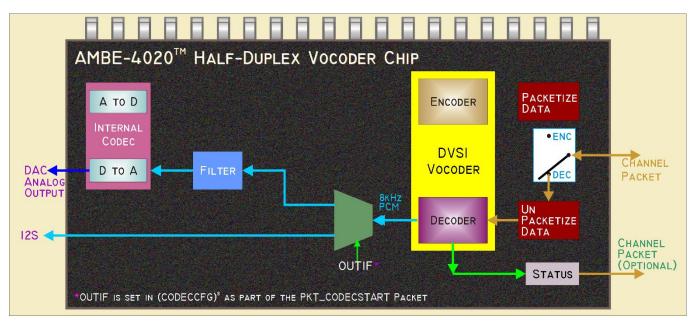

|   |                   | 2.3 Decoder Codec Mode                                                                    |    |

|   |                   | 2.4 Decoder Codec Passthru Mode                                                           |    |

|   |                   | 2.5 Full duplex Codec Mode                                                                |    |

|   |                   | <ul> <li>2.6 Push-to-Talk Codec Mode</li> <li>2.7 Skew Control in Codec Mode</li> </ul>   |    |

|   |                   | 2.7 Skew Control in Codec Mode<br>2.8 Timing of transmitted channel packets in Codec Mode |    |

|   |                   | 2.9 Timing of received channel packets in Codec Mode (Channel Packet Buffering)           |    |

|   | 5.3               | Switching between Packet Mode and Codec Mode                                              |    |

| ~ |                   |                                                                                           |    |

| 6 | VO                | CODER CONTROL/STATUS FLAGS                                                                | 65 |

| 7  | PACKET FORMATS                                                                                | 68  |

|----|-----------------------------------------------------------------------------------------------|-----|

|    | 7.1 Packet Interface Overview                                                                 |     |

|    | 7.2 Packet Interface Format                                                                   |     |

|    | 7.2.1 START_BYTE (1 byte)                                                                     |     |

|    | 7.2.2 LENGTH (2 bytes)                                                                        |     |

|    | 7.2.3 <i>TYPE</i> (1 byte)                                                                    |     |

|    | 7.2.4 Packet Fields                                                                           |     |

|    | 7.3 Packet Field Reference                                                                    |     |

|    | 7.3.1 Packet Field Nomenclature Key                                                           |     |

|    | 7.3.2 Control Packet Format                                                                   |     |

|    | 7.3.3 Input Speech Packet Format                                                              |     |

|    | <ul><li>7.3.4 Output Speech Packet Format</li><li>7.3.5 Input Channel Packet Format</li></ul> |     |

|    | 7.3.6 Output Channel Packet Format0                                                           |     |

|    | L L                                                                                           |     |

|    | 7.4 Example Packets                                                                           |     |

|    | 7.4.1       Speech Packet Example 1         7.4.2       Speech Packet Example 2               |     |

|    | 7.4.2 Speech Packet Example 2<br>7.4.3 Channel Packet Example 1                               |     |

|    | 7.4.4 Channel Packet Example 2                                                                |     |

| 8  | APPENDICES                                                                                    | 106 |

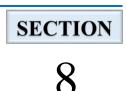

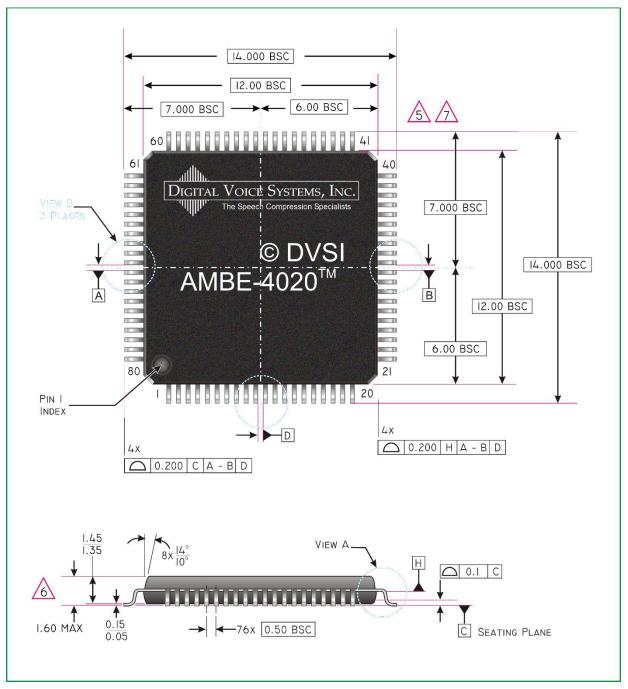

| Ū  | 8.1 80-pin Low-Profile Quad Flat Pack (LQFP) Package Details                                  |     |

|    | 8.2 Total Algorithmic Delay                                                                   |     |

|    | 8.3 Vocoder Rate by Index Number                                                              |     |

|    | 8.4 Schematics                                                                                | 111 |

| 9  | SUPPORT                                                                                       |     |

|    | 9.1 DVSI Contact Information                                                                  | 114 |

| 10 | ENVIRONMENTAL AND COMPLIANCE INFORMATION                                                      | 115 |

| 11 | IC CHIP SOFTWARE ERRATA                                                                       | 116 |

| 12 | HISTORY OF REVISIONS                                                                          |     |

## List of Figures

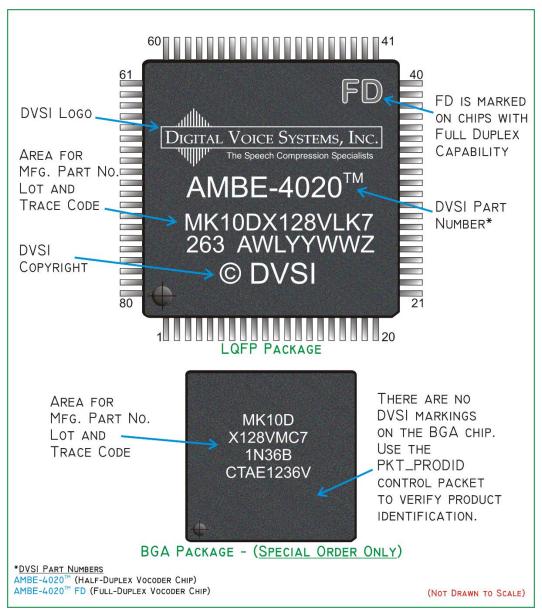

| Figure 1 AMBE-4020 <sup>™</sup> Half-Duplex and Full-Duplex Vocoder Chip Markings      | 3  |

|----------------------------------------------------------------------------------------|----|

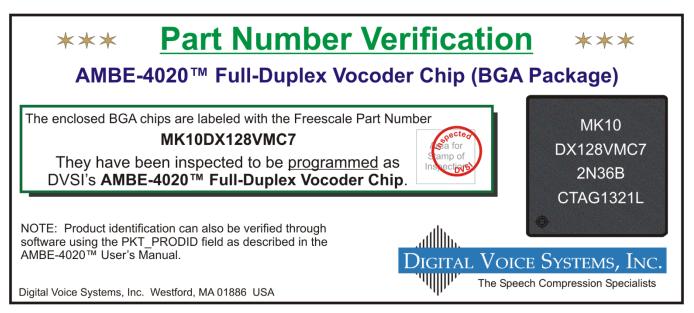

| Figure 2 ABME-4020 <sup>™</sup> Shipping Tray Label for Special Order BGA chip only    | 4  |

| Figure 3 AMBE-4020 <sup>™</sup> Package Label example for Special Order BGA chip only  | 4  |

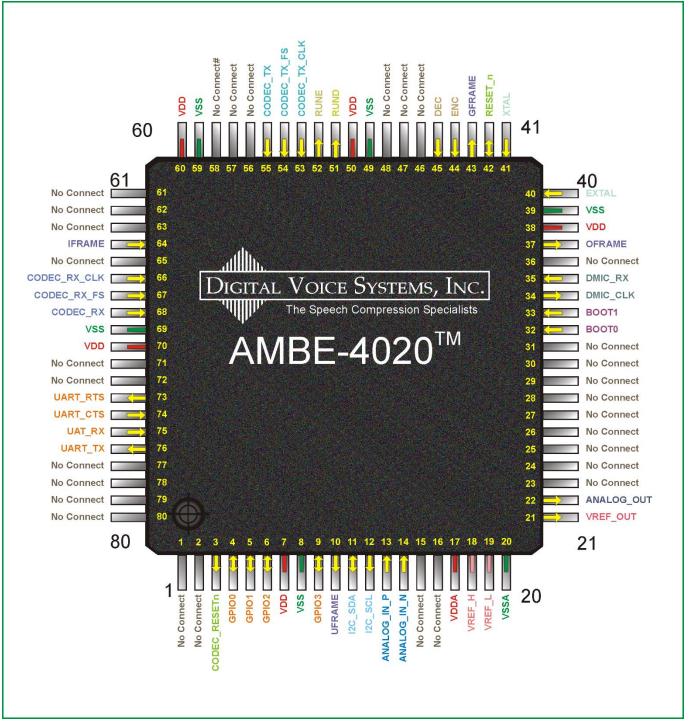

| Figure 4 AMBE-4020 <sup>™</sup> Vocoder Chip Pins for LQFP Package                     | 5  |

| Figure 5 AMBE-4020 <sup>™</sup> Vocoder Chip Pins for BGA Package (Special Order Only) | 6  |

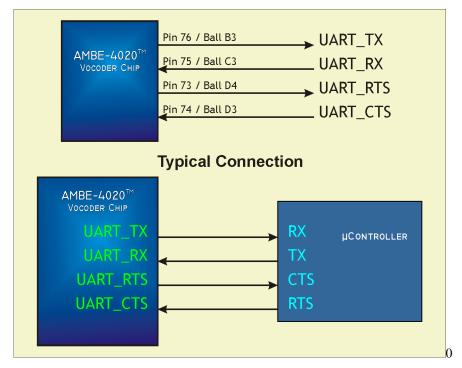

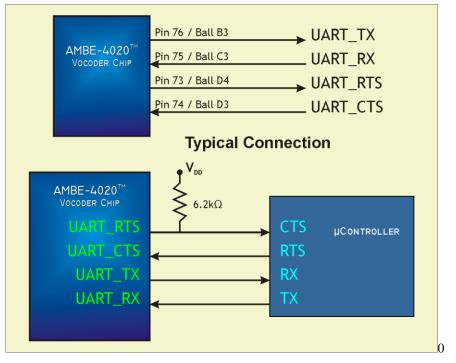

| Figure 6 UART Connection                                                               | 10 |

| Figure 7 UART with 6.2kOhm Pull-up Resistor Connection                                 | 11 |

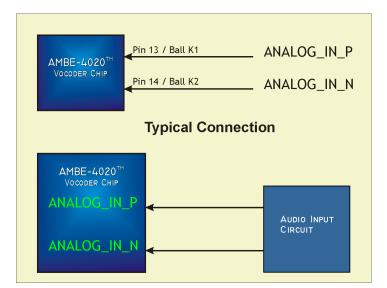

| Figure 8 ADC Connection (For more details see schematic in Section 8.4)                |    |

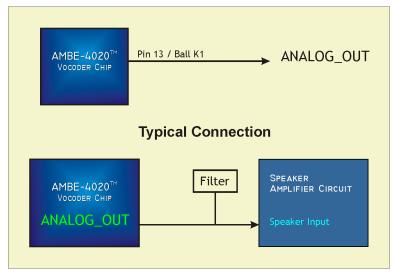

| Figure 9 DAC Connection                                                                | 13 |

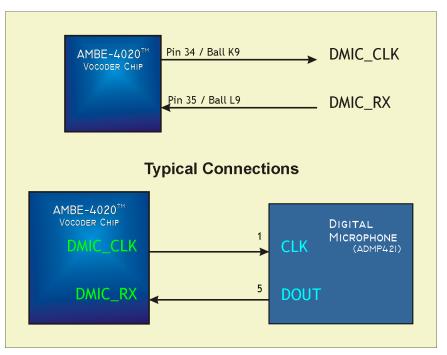

| Figure 10 DMIC Connection (For more details see schematic in Section 8.4)              | 14 |

| Figure 11 DMIC Timing                                                                  |    |

| Figure 12 I2S Connection                                           |     |

|--------------------------------------------------------------------|-----|

| Figure 13 I2S Timing diagram                                       |     |

| Figure 14 I2C Connection                                           |     |

| Figure 15 Internal Oscillator Crystal/Ceramic Resonator            | 23  |

| Figure 16 External Clock Connection                                |     |

| Figure 17 OFRAME Frame Interval                                    |     |

| Figure 18 UFRAME                                                   |     |

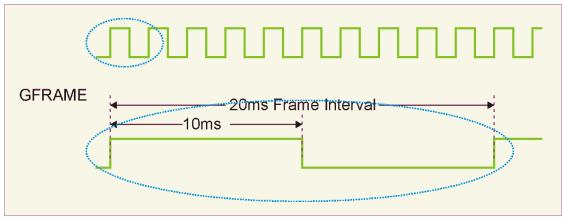

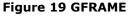

| Figure 19 GFRAME                                                   |     |

| Figure 20 AMBE-4020™ Clocking                                      |     |

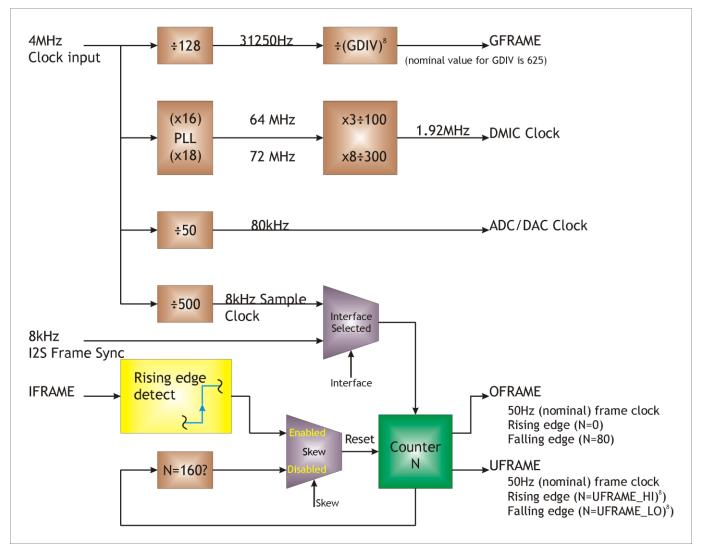

| Figure 21 Input signal measurement reference                       |     |

| Figure 22 Reset Timing                                             |     |

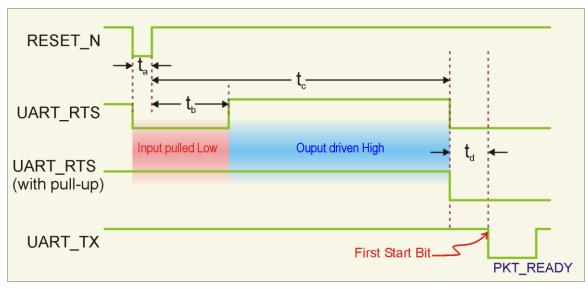

| Figure 23 Power mode state transition diagram                      |     |

| Figure 24 Power Consumption Half-Duplex (1.8V Supply)              |     |

| Figure 25 Power Consumption Half-Duplex (3.3V Supply)              |     |

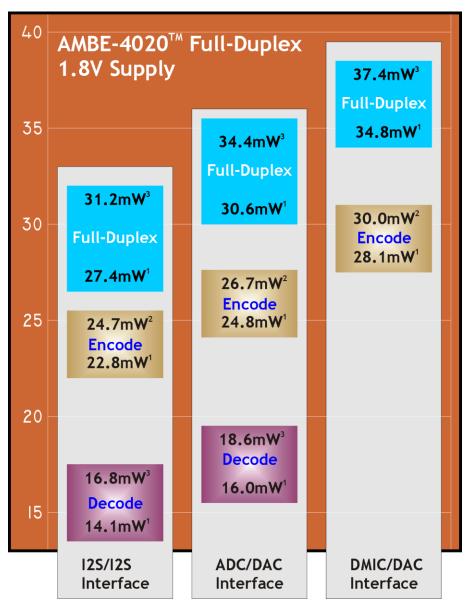

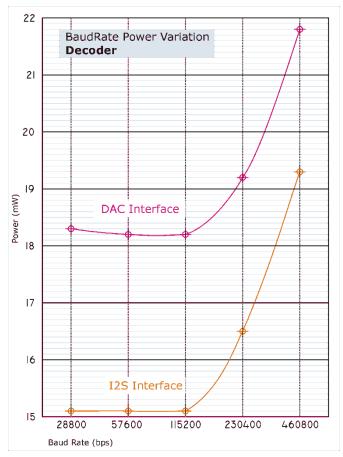

| Figure 26 Power Consumption Full-Duplex (1.8V Supply)              |     |

| Figure 27 Power Consumption Full-Duplex (3.3V Supply)              |     |

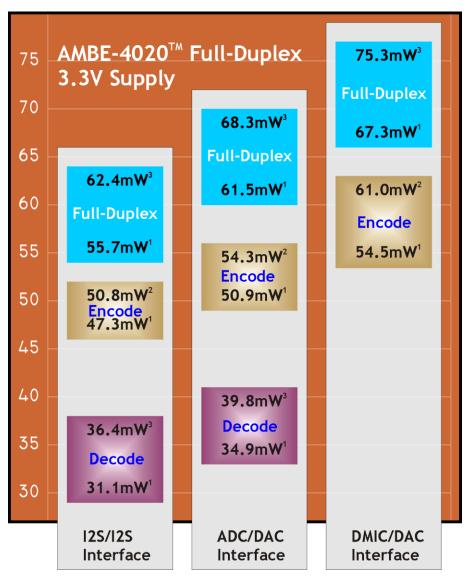

| Figure 28 Codec Mode Power Variation with Baud Rate                |     |

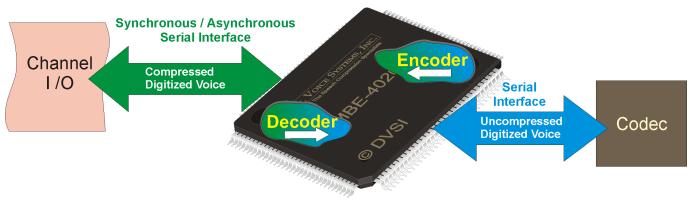

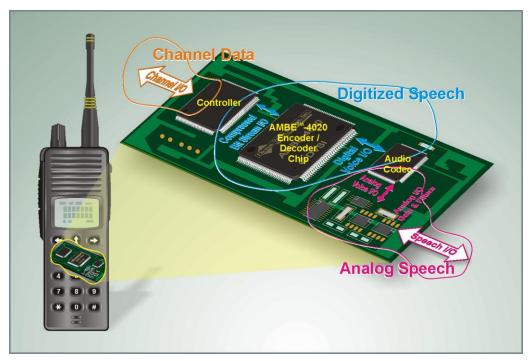

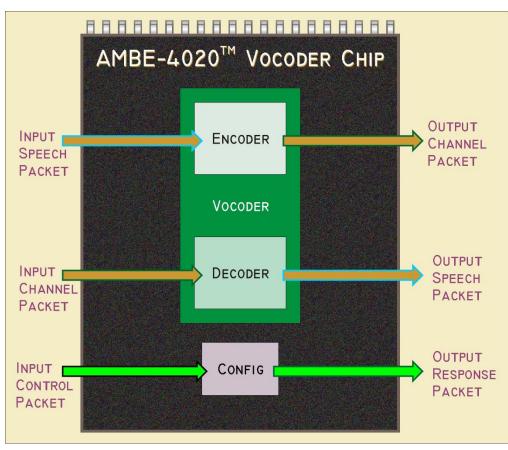

| Figure 29 Basic Operation                                          |     |

| Figure 30 Typical Vocoder Implementation                           | 46  |

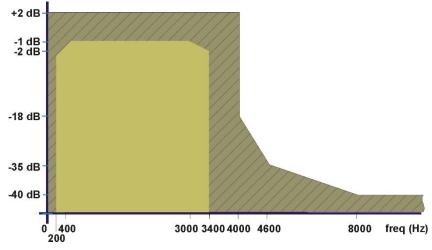

| Figure 31 Front End Input Filter Mask                              |     |

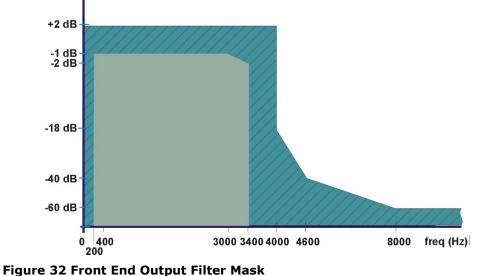

| Figure 32 Front End Output Filter Mask                             | 47  |

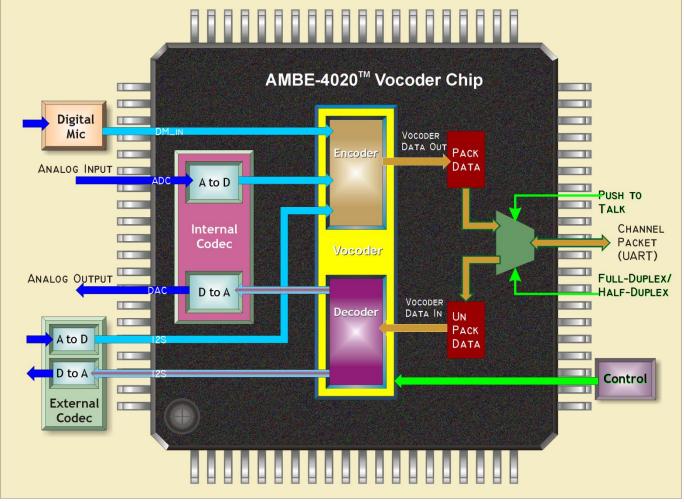

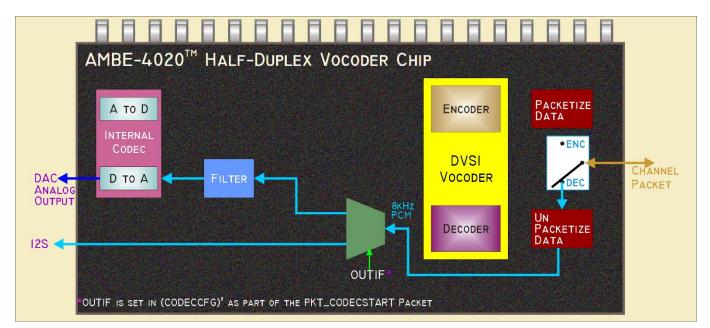

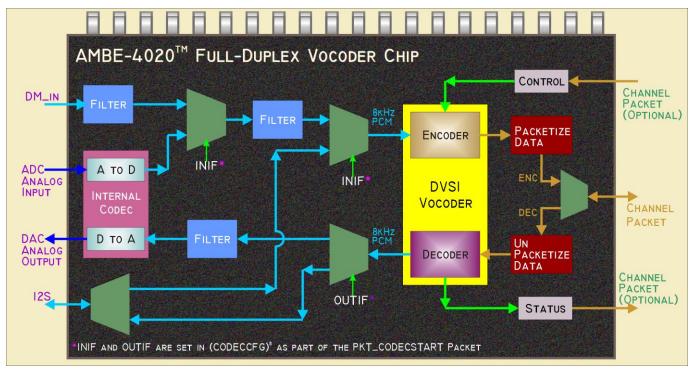

| Figure 33 AMBE-4020™ Block Diagram                                 |     |

| Figure 34 Packet Mode                                              |     |

| Figure 35 Encoder Codec Mode                                       |     |

| Figure 36 Encoder Pass thru mode                                   |     |

| Figure 37 Decoder Codec Mode                                       |     |

| Figure 38 Decoder Passthru Mode                                    | 58  |

| Figure 39 Full-Duplex Codec Mode                                   |     |

| Figure 40 OFRAME Timing                                            |     |

| Figure 41 Switching between Packet and Codec Modes                 |     |

| Figure 42 LQFP Mechanical Details                                  | 106 |

| Figure 43 LQFP layout Detail Views                                 |     |

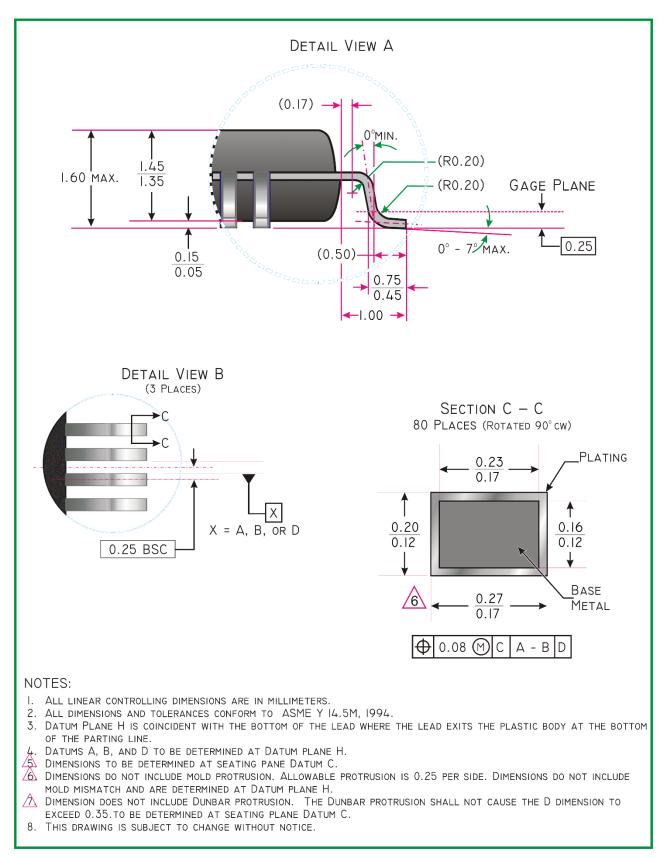

| Figure 44 BGA Mechanical Details (Only available on Special Order) | 108 |

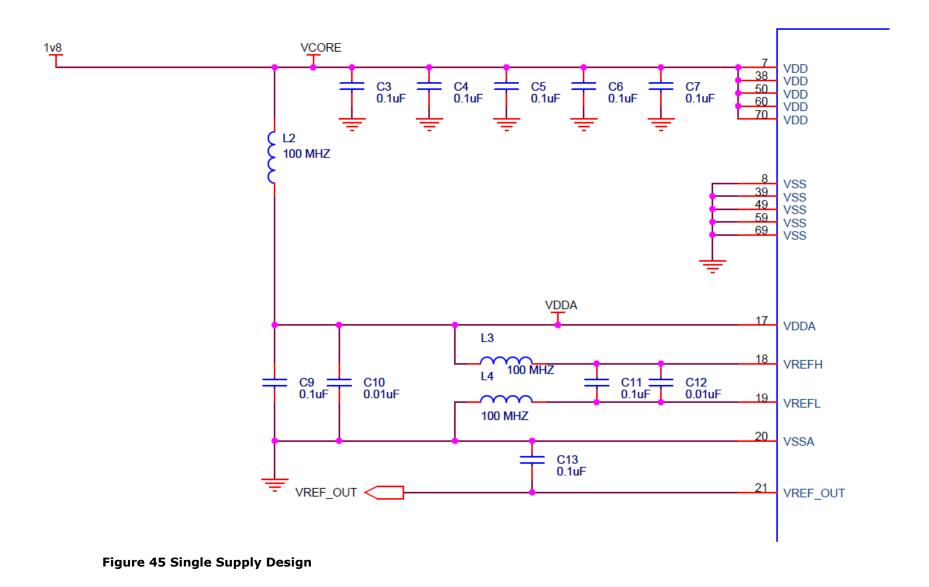

| Figure 45 Single Supply Design                                     |     |

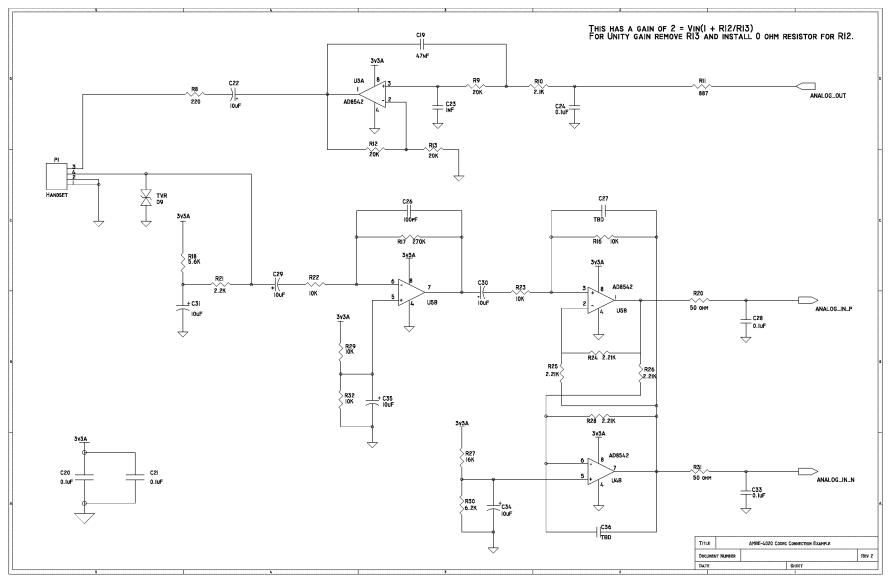

| Figure 46 AMBE-4020 <sup>™</sup> Codec connection example          |     |

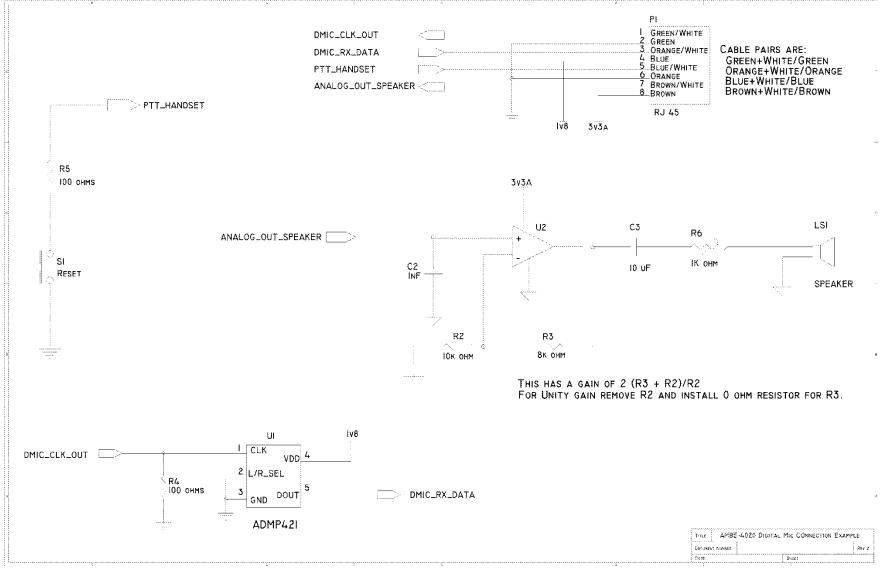

| Figure 47 AMBE-4020 <sup>™</sup> DMIC connection example           | 113 |

|                                                                    |     |

## List of Tables

| Table 1 Vocoder Interoperability                           | 1  |

|------------------------------------------------------------|----|

| Table 2 Pinout List                                        | 10 |

| Table 3 UART Interface Pins                                | 10 |

| Table 4 16-bit ADC Interface Pins                          | 12 |

| Table 5 12-bit DAC Interface Pins                          | 13 |

| Table 6 DMIC Interface Pins                                | 13 |

| Table 7 DMIC Timing                                        | 14 |

| Table 8 I2S Interface Pins                                 | 17 |

| Table 9 I2S Timing                                         |    |

| Table 10 I2C Interface Pins                                | 19 |

| Table 11: Parameters Specified for each Boot Configuration | 21 |

| Table 12: Factory Settings for each Boot Configuration     | 22 |

| Table 13: GPIO Interface Pins                              |    |

| Table 14 Input Clock Requirements                          | 24 |

|                                                            |    |

| Table 15: OFRAME/IFRAME/UFRAME/GFRAME Interface Pins                   | 25 |

|------------------------------------------------------------------------|----|

| Table 16 Moisture Sensitivity Rating                                   | 28 |

| Table 17 Electrostatic Discharge Ratings                               | 28 |

| Table 18 Pin Capacitance Attributes                                    | 28 |

| Table 19 Thermal Ratings                                               | 29 |

| Table 20 Thermal Operating Requirements                                | 29 |

| Table 21 Thermal Resistance Characteristics                            | 29 |

| Table 22 Normal Operating Conditions                                   | 30 |

| Table 23 Voltage and Current Operating Ratings                         | 30 |

| Table 24 Maximum Current Rating                                        |    |

| Table 25 Voltage and Current Operating Requirements                    | 32 |

| Table 26 Voltage and Current Operating Behaviors                       |    |

| Table 27 Reset Timing                                                  |    |

| Table 28 Wake Timing                                                   |    |

| Table 29 Power Mode States                                             |    |

| Table 30 Power mode state transitions                                  | 36 |

| Table 31 Typical Consumption from VDD during Codec Mode                | 43 |

| Table 32 Codec Mode Power Variation with Baud Rate                     |    |

| Table 33 Additional Power Consumption from VDD by Echo Canceller       |    |

| Table 34 Power Consumption from VDD and VDDA during Power Saving Modes |    |

| Table 35 Power Consumption from VDDA                                   |    |

| Table 36 In-band Tone Signaling Support                                |    |

| Table 37 Soft Decision Error Correction                                |    |

| Table 38: ENC/DEC combinations for Push-to-Talk Codec Mode             |    |

| Table 39: Skew Control Scenarios                                       |    |

| Table 40 ECONTROL Flags                                                |    |

| Table 41 ECONTROL Flags Description                                    |    |

| Table 42 ESTATUS Flags                                                 |    |

| Table 43 ESTATUS Flags Description                                     |    |

| Table 44 DCONTROL Flags                                                |    |

| Table 45 DSTATUS Flags                                                 |    |

| Table 46 DSTATUS Flags Description                                     |    |

| Table 47 General Packet Format                                         | 68 |

| Table 48 Packet Types                                                  |    |

| Table 49 General Field Format                                          |    |

| Table 50 Packet Fields                                                 |    |

| Table 51 PKT COMPAND Field Options                                     |    |

| Table 52 PKT_INIT Field                                                |    |

| Table 53 PKT_PMODE Field Settings                                      |    |

| Table 54 PKT_STARTCODEC Fields                                         |    |

| Table 55 PKT_CHANFMT Fields                                            |    |

| Table 56 PKT_SPCHFMT Fields                                            |    |

| Table 57 PKT ERROR Names                                               |    |

| Table 58 PKT_BOOTCFG                                                   |    |

| Table 59 PKT_GPIO Function Description                                 |    |

| Table 60 TONE Index Values                                             |    |

| Table 61 TONE Amplitude Values                                         |    |

| Table 62 Control Packet Fields                                         |    |

| Table 63 Input Speech Packet Fields                                    |    |

| Table 64 Output Speech Packet Fields                                   |    |

| Table 65 Input Channel Packet Fields                                   |    |

| Table 66 Output Channel Packet Fields                                  |    |

| Table 67 Speech Packet Example 1                                       |    |

|                                                                        |    |

| Table 68 Speech Packet Example 2  | 103 |

|-----------------------------------|-----|

| Table 69 Channel Packet Example 1 |     |

| Table 70 Channel Packet Example 2 | 104 |

| Table 71 Rate Index Numbers       |     |

Product Introduction

SECTION

## 1 Product Introduction

Digital Voice System's AMBE-4020<sup>TM</sup> Vocoder Chip is an extremely flexible, low cost, half-duplex, voice compression solution that is ideal for commercial, consumer, and military mobile radio communication applications. As part of DVSI's family of high performance vocoder chips, the AMBE-4020<sup>TM</sup> Vocoder Chip boasts a built-in 16-bit ADC and 12-bit DAC in a small footprint design that makes it easy to integrate and requires minimal power.

The AMBE-4020<sup>TM</sup> Vocoder Chip uses proven technology to deliver a level of performance and reliability typically associated only with customized ASICs, but without the associated risks and high development costs. With small quantity, off-the-shelf availability and no licensing fees or royalties, engineers and original equipment manufacturers are able to efficiently design and affordably produce high performance, narrowband, communication equipment.

There are two versions of the AMBE-4020<sup>TM</sup> Vocoder Chip. The AMBE-4020<sup>TM</sup> Full-Duplex is a full-duplex version and the AMBE-4020<sup>TM</sup> is a half-duplex vocoder chip. Both models are similar to each other except a few minor differences. The manual will call out the functions that are unique to each model using colored text. Orange for the AMBE-4020<sup>TM</sup> Full-Duplex and Green for the AMBE-4020<sup>TM</sup> Half-Duplex, where the black text is common to both devices. Both models are a compact LQFP package (BGA package available on Special Order).

## 1.1 Advances in Vocoder Design

The AMBE-4020<sup>™</sup> Vocoder Chip implements DVSI's patented AMBE+2<sup>™</sup> Voice Compression Algorithm that can operate at virtually any data rate from 2.0 to 9.6 kbps. When enabled, the built-in FEC combines block and convolution codes with optional four-bit soft decision decoding.

With this high degree of flexibility, the user can optimize speech and Forward Error Correction (FEC) rates to provide exceptional robustness to background noise and intelligible speech in degraded channel conditions, even with bit errors (BER) of up to 20%. This level of performance can lead to the successful development and deployment of wireless communication systems in the most demanding environments.

As another member DVSI's family of advanced voice compression products, the AMBE-4020<sup>TM</sup> has interoperable modes that provide a seamless migration path from systems already using DVSI's AMBE-3000<sup>TM</sup> and AMBE-2000<sup>TM</sup> Vocoder Chips.

| DVSI Vocoders Interoperable with the AMBE-4020 <sup>TM</sup> |       |  |  |  |  |  |  |

|--------------------------------------------------------------|-------|--|--|--|--|--|--|

| AMBE-2000 <sup>™</sup> Chip Rates                            | YES   |  |  |  |  |  |  |

| AMBE-3000 <sup>™</sup> Chip Rates*                           | MOST* |  |  |  |  |  |  |

| MotoTRBO                                                     | NO    |  |  |  |  |  |  |

| DMR                                                          | NO    |  |  |  |  |  |  |

| dPMR                                                         | NO    |  |  |  |  |  |  |

| DSTAR                                                        | YES   |  |  |  |  |  |  |

| NXDN                                                         | NO    |  |  |  |  |  |  |

| APCO Project 25 Half Rate                                    | NO    |  |  |  |  |  |  |

| APCO Project 25 Full Rate                                    | NO    |  |  |  |  |  |  |

| TerreStar                                                    | NO    |  |  |  |  |  |  |

| MexSat                                                       | NO    |  |  |  |  |  |  |

| GlobalStar                                                   | NO    |  |  |  |  |  |  |

| BGAN                                                         | NO    |  |  |  |  |  |  |

### Table 1 Vocoder Interoperability

\* **NOTE:** The following AMBE-3000<sup>TM</sup> built-in rates are not supported: 33-37, 47, and 51-55. As a result, MotoTRBO, DMR, dPMR, NXDN and APCO Project 25 Half Rate are supported by the AMBE-3000<sup>TM</sup>, but are not supported by the AMBE-4020<sup>TM</sup>.

## 1.2 AMBE-4020<sup>™</sup> Vocoder Chip Performance

The AMBE-4020<sup>™</sup> Vocoder Chip offers designers several convenient features. In Addition to the built-in 16-bit ADC and 12bit DAC, there is an interface for low-cost digital microphone, automatic Voice/Silence Detection (VAD), adaptive comfort noise insertion (CNI), DTMF and Call Progress Tone detection/regeneration, and low power modes. Additionally, the AMBE-4020<sup>™</sup> Vocoder Chip includes serial interfaces for vocoder configuration, status information, as well as, transferring speech and compressed data bits to/from the chip's encoder and decoder. The numerous advanced design features not only ease design constraints, but also reduces additional hardware requirements.

The AMBE-4020<sup>TM</sup> vocoder chip offers our customers tremendous flexibility in the design of high performance, narrowband, push-to-talk equipment. This small, low-cost platform enables engineers and Original Equipment Manufacturers to efficiently produce mobile radio and other wireless communication solutions where bandwidth is at a premium and high quality voice is crucial to success.

- Superior voice quality, DVSI's latest generation AMBE+2<sup>TM</sup> Vocoder Technology

- The AMBE-4020<sup>™</sup> Full-Duplex supports echo cancellation and echo suppression

- Maximizes channel bandwidth efficiency by supporting data-rates from 2.0 kbps to 9.6 kbps

- User selectable forward error correction rates 50 bps to 7.2 kbps (total rate not exceeding 9.6 kbps)

- Excellent performance at low data rates and harsh environments

- Robustness to acoustic background noise and channel bit errors

- Advanced features like Noise Suppression, Improved Error Mitigation, and Soft Decision FEC Decoding

- Supports a-law and µ-law companding via I2S interface

- DTMF and single tone detection and regeneration with North American call progress tones

## 1.3 Design Flexibility/Low Cost Integration

The AMBE-4020<sup>TM</sup> Vocoder Chip includes a number of advanced features that are combined with low power consumption to offer the affordability, mobility and power efficiency required by virtually all mobile communication devices.

- Complete integrated 16-bit ADC and 12-bit DAC and vocoder in one chip

- Works with most low-cost A/D-D/A codecs

- Input Interfaces available: internal ADC or digital mic or I2S

- Output interfaces available: internal DAC or I2S

- Interface for low-cost digital microphone

- Very low power consumption Ideal for portable mobile devices

- 80 pin 12mm x 12mm LQFP small package design

- 121 ball 8mm x 8mm BGA package available only on special order

- Push-to-talk signaling

- Half-duplex Operation or Full-duplex Operation

- No licensing fees or royalties

- Off-the-shelf availability for quick delivery

## 1.4 Proven Technology

The value of DVSI's AMBE® Technology goes beyond low bit rate and voice quality. It has been thoroughly evaluated and tested by international manufacturers under various conditions using a variety of languages. This assures the user is getting the best vocoder available and makes the DVSI vocoder the logical choice for all your voice compression needs. DVSI has been providing Voice Compression technology for more than 25 years. DVSI's technology has been proven a key component in the overall success of communication systems worldwide.

Hardware Information

# SECTION

## 2 Hardware Information

The AMBE-4020<sup>TM</sup> Vocoder Chip provides excellent performance with the latest low power innovations and high precision mixed-signal capability.

## 2.1 AMBE-4020<sup>™</sup> and AMBE-4020<sup>™</sup> Full-Duplex Vocoder Chip Markings

DVSI Logo --- Representation of Digital Voice Systems, Inc. Logo. DVSI Part Number --- The DVSI device part number is AMBE-4020<sup>TM</sup> © DVSI --- Copyright Digital Voice Systems, Incorporated

## 2.2 AMBE-4020<sup>™</sup> BGA Packaging labeling

The AMBE-4020<sup>TM</sup> Vocoder chip is available in a <u>BGA package only as a Special Order</u>. When a BGA chip is shipped, to clearly indicate what AMBE-4020<sup>TM</sup> version is shipped to our customers, there is a verification label included on the tray of the vocoder chip shipment. An example of the AMBE-4020<sup>TM</sup> Vocoder chip container tray notice for the AMBE-4020<sup>TM</sup> Full-Duplex (BGA package) is shown in Figure 2.

Figure 2 ABME-4020<sup>™</sup> Shipping Tray Label for <u>Special Order BGA chip only</u>.

As an additional measure, the sealed package of AMBE-4020<sup>™</sup> BGA vocoder chips will have another notice to indicate the chips were verified to be programed correctly. An example of the AMBE-4020<sup>™</sup> Full Duplex (BGA package) notice that is placed on the outside of the package is shown in Figure 3.

Figure 3 AMBE-4020<sup>™</sup> Package Label example for <u>Special Order BGA chip only.</u>

## 2.3 LQFP Pin Assignments

Figure 4 AMBE-4020<sup>™</sup> Vocoder Chip Pins for LQFP Package

## 2.4 BGA Pin Assignments (Special Order Only)

|   |                 | 2                | 3            | 4     | 5      | 6      | 7                | 8     | 9                | 10              |         |

|---|-----------------|------------------|--------------|-------|--------|--------|------------------|-------|------------------|-----------------|---------|

| L | NC              | NC               | VREF<br>_OUT | NC    | NC     | vss    | NC               | BOOT1 |                  | VDD             | EXTAL   |

| Κ | ANALOG<br>_IN_P | ANALOG           | NC           | NC    | DAC    | NC     | NC               | BOOTO | DMIC_CLK         | VSS             | XTAL    |

| J | NC              | NC               | NC           | NC    | NC     | NC     | NC               | NC    | NC               | CODEC<br>_RX_FS | RESET_n |

| Η | NC              | NC               | NC           | NC    | NC     | NC     | GPI01            | NC    | NC               | OFRAME          | NC      |

| G | I2C_<br>SDA     | I2C_<br>SCL      | vss          | GPIO2 | VREF_H | VREF_L | vss              | NC    | DEC              | ENC             | GFRAME  |

| F | GPIO3           | UFRAME           | NC           | GPI00 | VDDA   | VSSA   | vss              | NC    | NC               | NC              | NC      |

| Ε | NC              | CODEC<br>_RESETn | NC           | NC    | VDD    | VDD    | VDD              | NC    | RUNE             | NC              | NC      |

| D | NC              | NC               |              |       | NC     | NC     | NC               | NC    | CODEC<br>_TX_CLK | NC              | NC      |

| С | NC              | NC               | UART_RX      | NC    |        | NC     | CODEC<br>_RX_CLK | NC    | CODEC<br>_TX_FS  | NC              | NC      |

| В | NC              | NC               | UART_TX      | NC    | NC     | NC     | IFRAME           | NC    | CODEC            | RUND            | NC      |

| Α | NC              | NC               | NC           | NC    | NC     | NC     | NC               | NC    | NC               | NC              | NC      |

|   |                 | 2                | 3            | 4     | 5      | 6      | 7                | 8     | 9                | 10              |         |

|   |                 |                  |              | BG    | A Bo   | otton  | ı Viev           | N     |                  |                 |         |

Figure 5 AMBE-4020<sup>™</sup> Vocoder Chip Pins for BGA Package (<u>Special Order Only</u>)

## 2.5 Pin Out Table

| Pin Name                                                | Pin Number |                                                                                                                                                                         | Pin    | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|---------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                         | LQFP       | BGA                                                                                                                                                                     | Туре   | 10005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                         |            |                                                                                                                                                                         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| CODEC_RESETn                                            | 3          | E2                                                                                                                                                                      | Output | Output to Reset an external Codec. This signal is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| GPIO0                                                   | 4          | F4                                                                                                                                                                      | I/O    | The GPIO0-GPIO3 pins are controlled using a control packet (PKT_GPIO). The packet allows the direction of each pin to                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| GPIO1                                                   | 5          | H7                                                                                                                                                                      | I/O    | be specified independently. It also allows the state for output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| GPIO2                                                   | 6          | G4                                                                                                                                                                      | I/O    | pins to be specified and it allows for the state of input pins to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| GPIO3                                                   | 9          | F1                                                                                                                                                                      | I/O    | be returned in a response packet. The default state after reset is that GPIO0-GPIO3 are disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

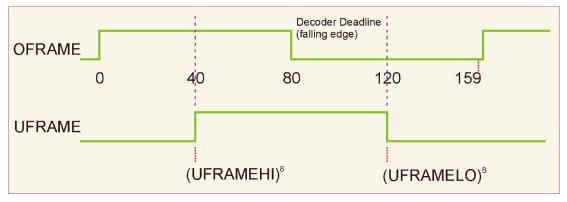

| UFRAME 10 F2                                            |            | F2                                                                                                                                                                      | Output | User Frame. This 50 Hz signal is synchronous with OFRAME and may be customized by the user. By default, The signal rises 5 ms after OFRAME rises and falls 5 ms after OFRAME falls, such that it looks like OFRAME delayed by a quarter cycle. The rise time and fall time are configurable in 125 $\mu$ s increments, such that both the delay and duty cycle can be configured. Another processor might use the signal to perform actions synchronously to the AMBE-4020 <sup>TM</sup> . The signal provides two edges that can be configured via a control packet (PKT_UFRAME). |  |  |  |

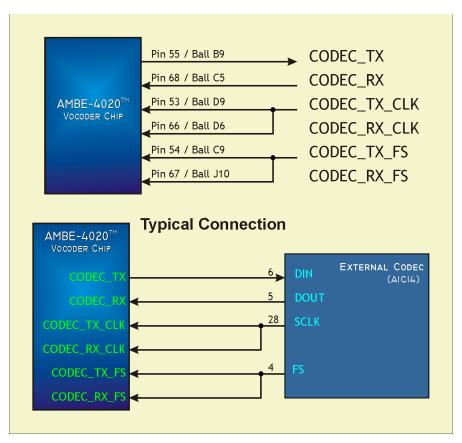

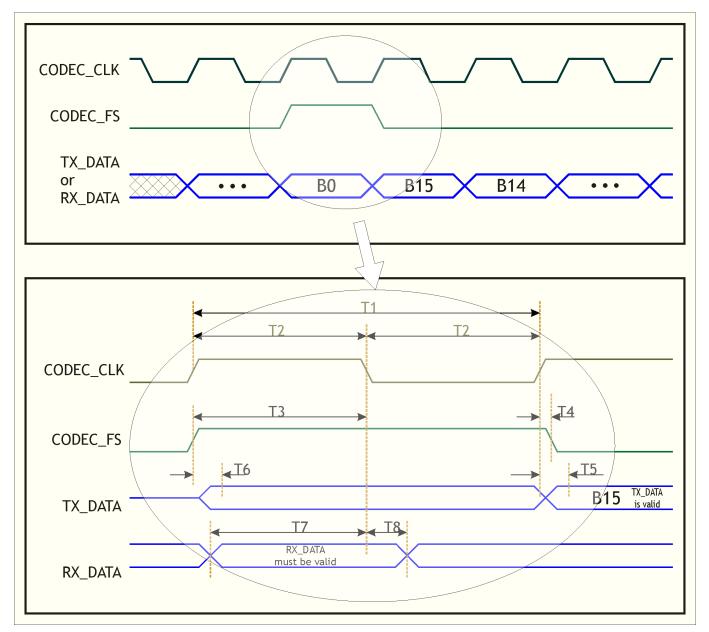

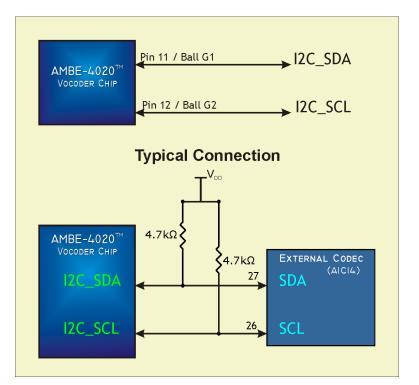

| I2C_SDA                                                 | 11         | G1                                                                                                                                                                      | I/O    | This pin is the data pin used to transfer configuration data to<br>an external codec using the I2C protocol. The pin is open<br>drain enabled and must be pulled high.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| I2C_SCL12G2I/OThis pin is the<br>an external coordinate |            | This pin is the clock pin used to transfer configuration data to<br>an external codec using the I2C protocol. The pin is open<br>drain enabled and must be pulled high. |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ANALOG_IN_P                                             | 13         | K1                                                                                                                                                                      | Input  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| ANALOG_IN_N                                             | 14         | K2                                                                                                                                                                      | Input  | These pins are the internal ADC's differential input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| VDDA                                                    | 17         | F5                                                                                                                                                                      | Power  | Analog supply voltage: This can be connected to the same<br>supply as VDD but should be isolated to minimize noise and<br>error. See Drawing on page 111.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| VREFH                                                   | 18         | G5                                                                                                                                                                      | Input  | ADC positive reference voltage: This should be nominally the<br>same voltage as VDDA but should be isolated to minimize<br>noise and error. See Drawing on page 111. The voltage level<br>on this pin is used as a reference for ADC and DAC. Note:<br>this pin should be tied to VDD if the ADC and DAC are not<br>used.                                                                                                                                                                                                                                                          |  |  |  |

| VREFL                                                   | 19         | G6                                                                                                                                                                      | Input  | ADC negative reference voltage: This should be the same<br>voltage as VSS but should be isolated to minimize noise and<br>error. See Drawing on page 111. The level on this pin is used<br>as a reference for ADC and DAC.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VSSA                                                    | 20         | F6                                                                                                                                                                      | GND    | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| VREF_OUT                                                | 21         | L3                                                                                                                                                                      | Output | No connection required. Internally-generated Voltage<br>Reference output. When the ADC and/or DAC are active, the<br>nominal voltage level on this pin is 1.195V.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| ANALOG_OUT                                              | 22         | K5                                                                                                                                                                      | Output | Analog Output from the internal DAC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| BOOT0                                                   | 32         | K8                                                                                                                                                                      | Input  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| BOOT1        | 33 | L8  | Input  | BOOT0 and BOOT1 are used to select one of four boot<br>configurations. Boot Configuration 0 is hard-coded whereas<br>Boot Configurations 1-3 are stored in persistent memory and<br>may be customized using PKT_BOOTCFG.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|----|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

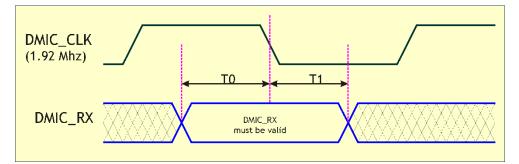

| DMIC_CLK     | 34 | К9  | Output | When the Digital Mic is selected as the codec mode input speech source, the AMBE-4020 <sup>TM</sup> outputs a 1.92 MHz clock on DMIC_CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DMIC_RX      | 35 | L9  | Input  | The AMBE-4020 <sup>™</sup> receives PDM speech data from a digital microphone. See Schematic on Page 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

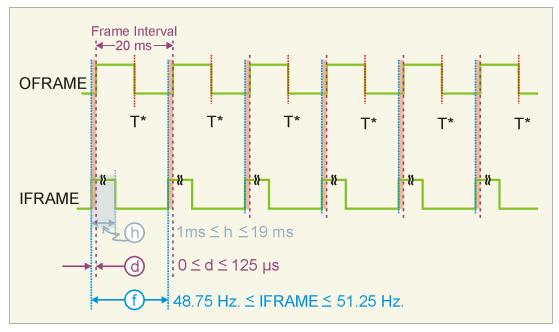

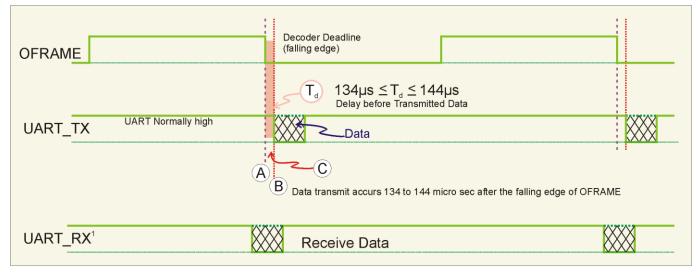

| OFRAME       | 37 | H10 | Output | A 50 Hz framing signal. In codec mode, the AMBE-4020 <sup>TM</sup> operates using 20 ms frames. The frame interval is the period between two successive rising edges of OFRAME. When the encoder is running, it outputs packets synchronously with OFRAME. The onset of packet transmission occurs between 134 $\mu$ s and 144 $\mu$ s after the falling edge of OFRAME. The falling edge of OFRAME also serves as the deadline for receiving a packet to be decoded. If no packets are available to decode at this deadline, then the chip will automatically insert a "repeat" frame that has small impact on voice quality when the frequency of repeats is low. The signal has a duty cycle of 50% $\pm$ 2.5%. |

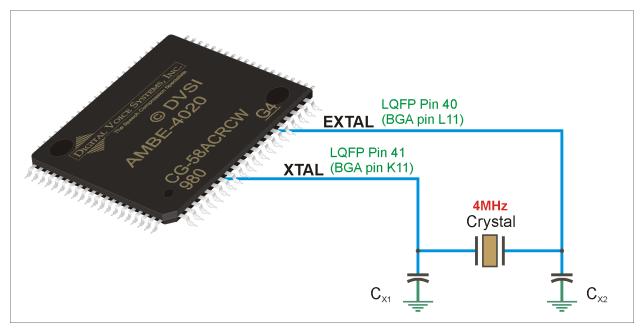

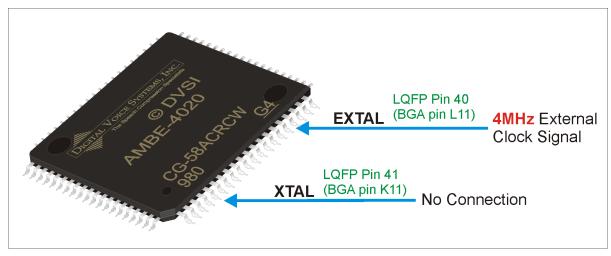

| EXTAL        | 40 | L11 | Input  | Use EXTAL/XTAL to connect a 4 Mhz Crystal/Clock input as                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |