# PM7540<sup>™</sup> Power Management IC

## **Device Specification (Preliminary Information)**

80-VD691-1 Rev. B

February 26, 2007

Submit technical questions at: https://support.cdmatech.com

### **QUALCOMM Confidential and Proprietary**

**Restricted Distribution.** Not to be distributed to non-employees of QUALCOMM or its subsidiaries without the express approval of Configuration Management.

Not to be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of QUALCOMM Incorporated.

QUALCOMM is a registered trademark and registered service mark of QUALCOMM Incorporated. Other product and brand names may be trademarks or registered trademarks of their respective owners. CDMA2000 is a registered certification mark of the Telecommunications Industry Association, used under license. ARM is a registered trademark of ARM Limited. QDSP is a registered trademark of QUALCOMM Incorporated in the United States and other countries.

Export of this technology may be controlled by the United States Government. Diversion contrary to U.S. law prohibited.

QUALCOMM Incorporated 5775 Morehouse Drive San Diego, CA 92121-1714 U.S.A.

Copyright © 2006, 2007 QUALCOMM Incorporated. All rights reserved.

# Contents

| 1 | Intro | duction    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|---|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1   | Documer    | ntation overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|   | 1.2   | Concise    | device description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |

|   | 1.3   |            | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|   | 1.4   | Terms an   | d acronyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 2 | Pin [ | Definition | is of the second s |    |

| 3 | Elect | trical Spe | ecifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|   | 3.1   | Absolute   | maximum ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|   | 3.2   | Recomm     | ended operating conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|   | 3.3   | Power su   | pply and digital logic characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30 |

|   | 3.4   | Multipur   | pose pin specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 3.5   | Input pov  | wer management specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   |       | 3.5.1      | External supply detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|   |       | 3.5.2      | USB_VBUS power source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |       | 3.5.3      | Input circuit transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|   |       | 3.5.4      | Transistor drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|   |       | 3.5.5      | Voltage regulation (VDD or VBAT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|   |       | 3.5.6      | Current regulation, monitoring, and over-current protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

|   |       | 3.5.7      | Pass transistor power limiting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|   |       | 3.5.8      | Main battery charging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |       | 3.5.9      | Coin cell charging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|   |       | 3.5.10     | Battery voltage alarm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |       | 3.5.11     | Under-voltage lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |       | 3.5.12     | Sudden momentary power loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   |       | 3.5.13     | VDD collapse protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 3.6   | Output v   | oltage regulation specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|   |       | 3.6.1      | Reference circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   |       | 3.6.2      | Switched-mode power supplies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 |

|   |       | 3.6.3      | Linear regulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

|   | 3.7   | General l  | nousekeeping specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59 |

|   |       | 3.7.1      | Analog multiplexer with offset and scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59 |

|   |       | 3.7.2      | System clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|   |       | 3.7.3      | Real-time clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 65 |

|   |       | 3.7.4      | Buffered VREF outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   |      | 3.7.5 Over-temperature protection (smart thermal control) |    |  |  |  |  |  |

|---|------|-----------------------------------------------------------|----|--|--|--|--|--|

|   | 3.8  | User interface specifications                             |    |  |  |  |  |  |

|   |      | 3.8.1 Current drivers                                     |    |  |  |  |  |  |

|   |      | 3.8.2 Vibration motor driver                              |    |  |  |  |  |  |

|   |      | 3.8.3 Speaker drivers                                     |    |  |  |  |  |  |

|   |      | 3.8.4 Video (TV) amplifier                                |    |  |  |  |  |  |

|   | 3.9  | IC-level interface specifications                         |    |  |  |  |  |  |

|   |      | 3.9.1 Power-on circuits and the power sequences           |    |  |  |  |  |  |

|   |      | 3.9.2 Serial bus interface                                |    |  |  |  |  |  |

|   |      | 3.9.3 Interrupt manager                                   |    |  |  |  |  |  |

|   |      | 3.9.4 Universal serial bus/on-the-go                      |    |  |  |  |  |  |

|   |      | 3.9.5 USB pins as an audio interface                      |    |  |  |  |  |  |

|   |      | 3.9.6 RUIM level translators                              |    |  |  |  |  |  |

| 4 | Mech | hanical Specifications                                    |    |  |  |  |  |  |

|   | 4.1  | Device physical dimensions                                |    |  |  |  |  |  |

|   | 4.2  | Device thermal characteristics                            |    |  |  |  |  |  |

|   | 4.3  | Device moisture sensitivity level                         |    |  |  |  |  |  |

|   | 4.4  | Device marking                                            |    |  |  |  |  |  |

| 5 | DCB  | Mounting Specifications                                   |    |  |  |  |  |  |

| 5 | 5.1  | Land pad and stencil design                               | 82 |  |  |  |  |  |

|   | 5.2  | Solder reflow                                             |    |  |  |  |  |  |

|   | 5.2  | SMT process verification                                  |    |  |  |  |  |  |

|   | 5.4  | Storage conditions, unpacking, and handling               |    |  |  |  |  |  |

|   | Э.т  | 5.4.1 Storage conditions.                                 |    |  |  |  |  |  |

|   |      | 5.4.2 Out-of-bag duration                                 |    |  |  |  |  |  |

|   |      | 5.4.3 Baking                                              |    |  |  |  |  |  |

|   |      | 5.4.4 Electrostatic discharge                             |    |  |  |  |  |  |

|   |      | č                                                         |    |  |  |  |  |  |

| 6 |      | king Methods and Materials                                |    |  |  |  |  |  |

|   | 6.1  | Tape and reel information                                 |    |  |  |  |  |  |

|   | 6.2  | Packing for shipment                                      |    |  |  |  |  |  |

|   | 6.3  | Packing materials                                         |    |  |  |  |  |  |

|   |      | 6.3.1 Shipping box barcode label                          |    |  |  |  |  |  |

|   |      | 6.3.2 Moisture barrier bag                                |    |  |  |  |  |  |

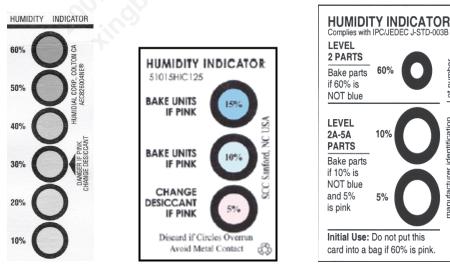

|   |      | 6.3.3 Humidity indicator cards                            |    |  |  |  |  |  |

| 7 | Part | Reliability                                               |    |  |  |  |  |  |

|   | 7.1  | Reliability qualification summary                         |    |  |  |  |  |  |

|   | 7.2  | Qualification sample description94                        |    |  |  |  |  |  |

## Figures

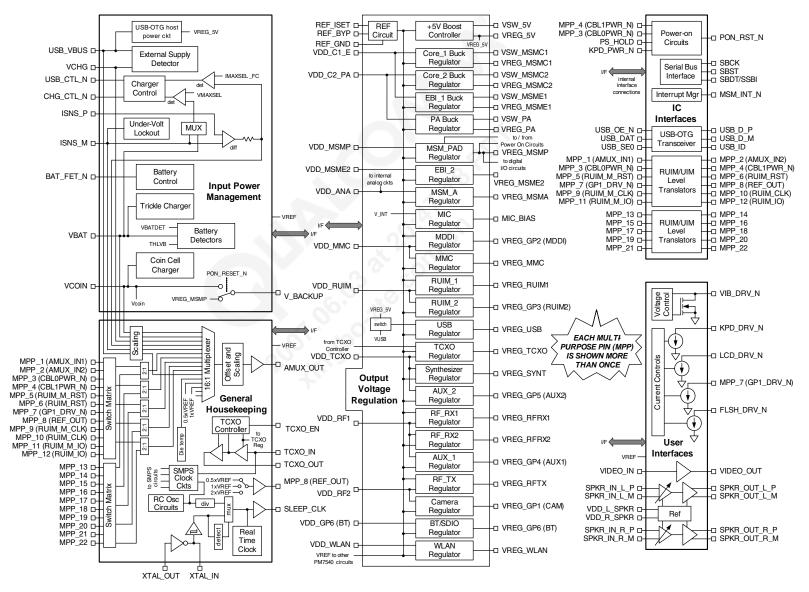

| Figure 1-1 | PM7540 functional block diagram                                | 10   |

|------------|----------------------------------------------------------------|------|

| Figure 2-1 | PM7540 IC pin assignments (top view)                           | . 16 |

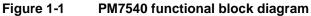

| Figure 3-1 | Typical MPP current sink performance for 20 mA setting         | 33   |

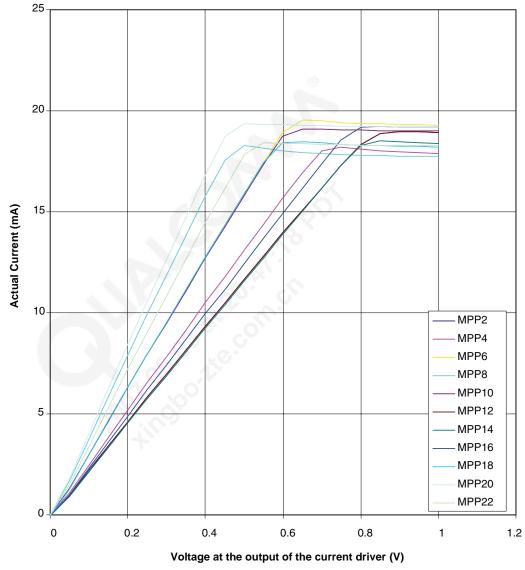

| Figure 3-2 | Typical MPP current sink performance for 40 mA setting         | 34   |

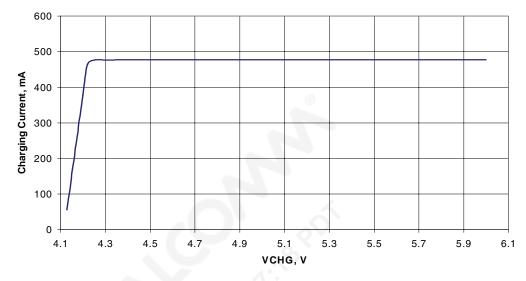

| Figure 3-3 | Example charging current vs. VCHG when VBAT = 4.1 V            |      |

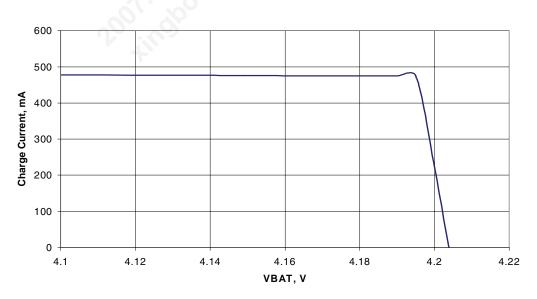

| Figure 3-4 | Example charging current vs. VBAT when VCHG = 5.0 V            | 43   |

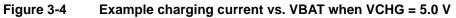

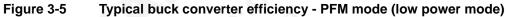

| Figure 3-5 | Typical buck converter efficiency - PFM mode (low power mode)  | . 53 |

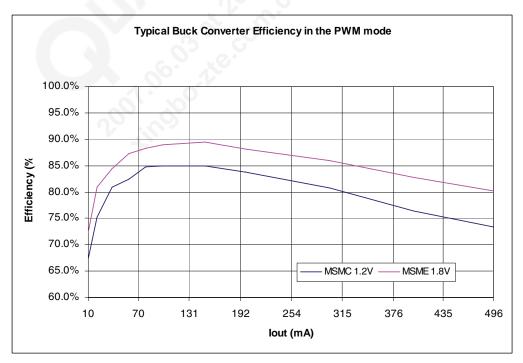

| Figure 3-6 | Typical buck converter efficiency - PWM mode (normal mode)     | 53   |

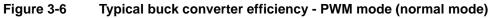

| Figure 3-7 | Typical VREG_MSMP load regulation                              | 56   |

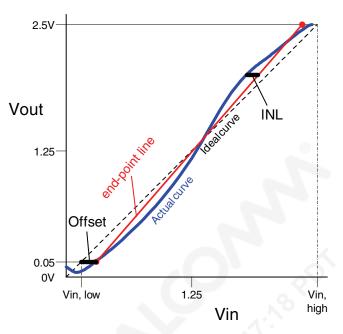

| Figure 3-8 | Multiplexer offset and gain errors                             | 62   |

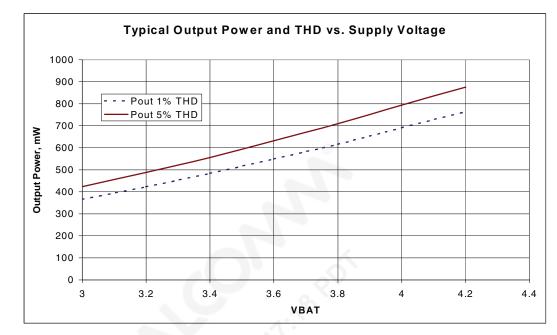

| Figure 3-9 | Speaker output power and THD vs. supply voltage                | 70   |

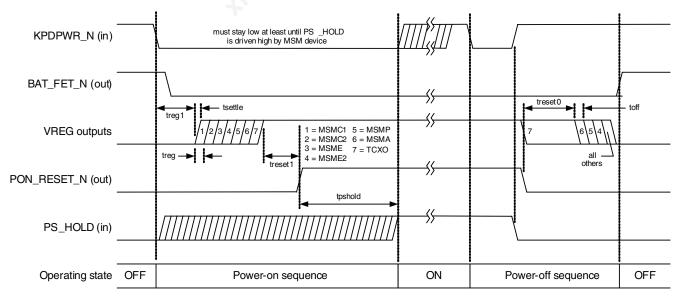

| -          | High-level power sequences timing diagram                      |      |

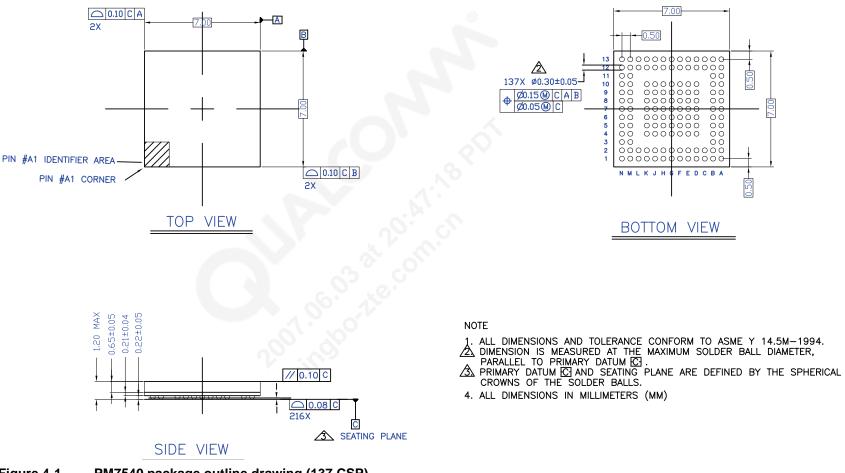

|            | PM7540 package outline drawing (137 CSP)                       |      |

| Figure 4-2 | PM7540 device marking (top view - not to scale)                | 81   |

| Figure 5-1 | Recommended 137 CSP land pattern (TBD)                         | 82   |

| Figure 5-2 | Recommended 137 CSP stencil pattern - square apertures (TBD)   | 83   |

| Figure 5-3 | Recommended 137 CSP stencil pattern - circular apertures (TBD) | 83   |

| Figure 6-1 | Carrier tape drawing with part orientation (TBD)               | 87   |

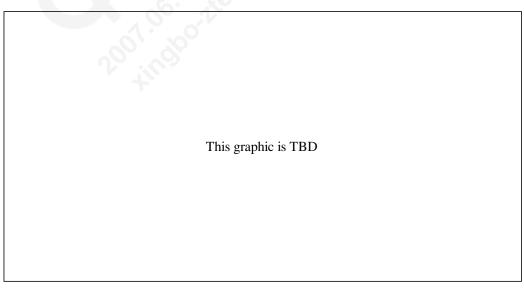

| <u> </u>   | Bag packing for tape and reel                                  |      |

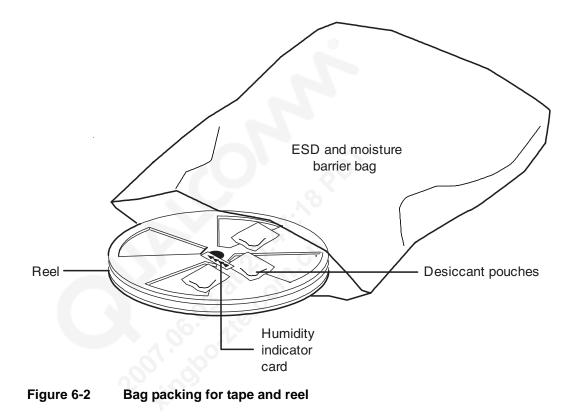

|            | Box packing for tape and reel                                  |      |

|            | Tape and reel box                                              |      |

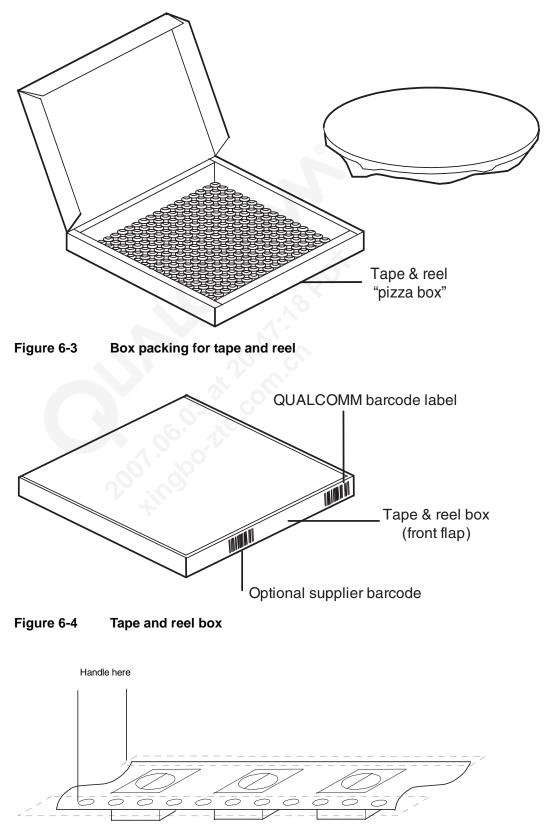

| -          | Tape handling                                                  |      |

|            | Barcode label example (TBD)                                    |      |

| -          | Caution label example                                          |      |

| Figure 6-8 | Example humidity indicator cards                               | 92   |

## Tables

| Table 1-1  | PM7540 documentation                                        | 8    |

|------------|-------------------------------------------------------------|------|

| Table 1-2  | Terms and acronyms                                          | .14  |

| Table 2-1  | PM7540 IC pin descriptions - listed in alpha-numeric order  | .17  |

| Table 2-2  | Input power management pin descriptions                     | . 19 |

| Table 2-3  | Output voltage regulation pin descriptions                  | . 20 |

| Table 2-4  | General housekeeping pin descriptions                       | . 22 |

| Table 2-5  | User interface pin descriptions                             | . 23 |

| Table 2-6  | IC-level interface pin descriptions                         | . 24 |

| Table 2-7  | Multipurpose pin descriptions                               | . 26 |

| Table 2-8  | Input power supply pin descriptions                         | . 27 |

| Table 2-9  | Ground pins                                                 | . 27 |

| Table 3-1  | Absolute maximum ratings                                    | . 28 |

| Table 3-2  | Recommended operating conditions                            | . 29 |

| Table 3-3  | DC characteristics                                          | . 30 |

| Table 3-4  | Multipurpose pin performance specifications                 |      |

| Table 3-5  | MPP pairs                                                   | .35  |

| Table 3-6  | External supply detection performance specifications        | .36  |

| Table 3-7  | USB_VBUS power source performance specifications            | .36  |

| Table 3-8  | Example external PNP charger pass transistor specifications | . 37 |

| Table 3-9  | Example external battery P-channel MOSFET specifications    | . 37 |

| Table 3-10 | External transistor driver specifications                   | . 38 |

| Table 3-11 | Voltage regulation performance specifications (VDD or VBAT) | . 39 |

| Table 3-12 | Current regulator/monitor performance specifications        | . 40 |

| Table 3-13 | Pass transistor power limiting performance specifications   | 41   |

| Table 3-14 | Trickle charging performance specifications                 | . 42 |

| Table 3-15 | Pulse charging performance specifications                   | . 45 |

| Table 3-16 | Coin cell charging performance specifications               | .45  |

| Table 3-17 | Backup voltage (V_BACKUP) performance specifications        | . 46 |

| Table 3-18 | Battery voltage alarm performance specifications            | . 46 |

| Table 3-19 | UVLO performance specifications                             | . 47 |

| Table 3-20 | SMPL performance specifications                             | . 47 |

| Table 3-21 | VDD collapse protection performance specifications          | . 47 |

|            | Voltage regulator summary                                   |      |

| Table 3-23 | Voltage reference performance specifications                | . 50 |

| Table 3-24 | Boost regulator performance specifications                  | 51   |

| Table 3-25 | Buck regulator performance specifications                   | . 52 |

| Table 3-26 | Linear regulator performance specifications - 300 mA rating | .54  |

| Table 3-27 | Linear regulator performance specifications - 150 mA rating | 56   |

| Table 3-28 | Linear regulator performance specifications - 150 mA rating | 58   |

|            | Regulator performance specifications - MIC bias             |      |

| Table 3-30 | Analog multiplexer inputs                                   | 60   |

| Offset and scaling performance specifications                  | 61                                                             |

|----------------------------------------------------------------|----------------------------------------------------------------|

| TCXO controller and buffer circuits performance specifications |                                                                |

| 32.768 kHz oscillator performance specifications               | 64                                                             |

| RC oscillator performance specifications                       | 64                                                             |

| SLEEP_CLK output performance specifications                    | 65                                                             |

| Current driver performance specifications                      | 67                                                             |

| Vibration motor driver performance specifications              |                                                                |

| Speaker driver performance specifications                      |                                                                |

| Video amplifier performance specifications                     |                                                                |

| Power-on circuit performance specifications                    | 72                                                             |

| USB-OTG transceiver performance specifications                 | 74                                                             |

| USB audio mode performance specifications                      | 76                                                             |

| Device thermal resistance                                      |                                                                |

| Device marking line descriptions                               |                                                                |

| Typical reflow profile conditions                              |                                                                |

| Stress tests                                                   |                                                                |

| Characteristics tests                                          |                                                                |

|                                                                |                                                                |

|                                                                | TCXO controller and buffer circuits performance specifications |

## **Revision history**

Bars appearing in the left margin of the document (as shown here) indicate changes made to this document since the last revision issued.

| Revision | Date                   | Description                                                                     |  |  |  |

|----------|------------------------|---------------------------------------------------------------------------------|--|--|--|

| А        | November 2006          | Initial release                                                                 |  |  |  |

| В        | February 2007          | Updated Table 3-25 for parameter for efficiency Iload                           |  |  |  |

|          |                        | Updated Table 3-37 for maximum short circuit current for vibration motor driver |  |  |  |

|          |                        | Updated Table 3-38 for:                                                         |  |  |  |

|          |                        | <ul> <li>Minimum input resistance</li> </ul>                                    |  |  |  |

|          | Minimum output voltage |                                                                                 |  |  |  |

|          |                        | <ul> <li>Maximum output voltage</li> </ul>                                      |  |  |  |

|          |                        | <ul> <li>Minimum mute suppression rating</li> </ul>                             |  |  |  |

# **1** Introduction

## **1.1 Documentation overview**

Technical information for the PM7540 IC is contained in the four documents listed in Table 1-1. Each document is a self-contained document that describes certain IC functions and/or specifications. Therefore, for a thorough understanding of the IC and its applications you will need to study all four documents. The device description given in the next section is a good place to begin learning about the PM7540 IC. All PM7540 documents are available for downloading for the QUALCOMM CDMA Tech Support website (https://support.cdmatech.com).

| Document #      | Title / description                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 80-VD691-1      | PM7540 Power Management IC Device Specification                                                                                                                                                                                                                                                                                                                                                   |

| (this document) | The primary objective of this document is to convey all PM7540 electrical and mechanical specifications. Additional material includes pin assignment definitions, PCB mounting specifications, packing methods and materials, and part reliability. This document can be used by company purchasing departments to facilitate procurement.                                                        |

| 80-VD691-3      | PM7540 Power Management IC User Guide                                                                                                                                                                                                                                                                                                                                                             |

|                 | This document provides detailed descriptions of all PM75402 functions and interfaces, defining how to control the IC and explaining the resulting operating modes.                                                                                                                                                                                                                                |

| 80-VD691-4      | PM7540 Power Management IC Revision Guide                                                                                                                                                                                                                                                                                                                                                         |

|                 | This document provides a history of PM7540 IC revisions and changes to its device specification. It explains how to identify the various IC revisions, discusses known issues for each revision and how to work around them, and lists performance specification changes between each revision of the <i>PM7540 Power Management IC Device Specification</i> (80-VD691-1).                        |

| 80-VD691-5      | PM7540 Power Management IC Design Guidelines                                                                                                                                                                                                                                                                                                                                                      |

|                 | This document tries to anticipate and answer questions hardware engineers<br>might have when incorporating the PM7540 IC into their wireless product<br>designs. An example application is presented, then specific design topics, such<br>as layout guidelines, power distribution recommendations, external component<br>recommendations, troubleshooting techniques, (and more) are addressed. |

This PM7540 Device Specification is organized as follows:

| Chapter 1 | Provides an overview of PM7540 documentation, gives a high-level functional description of the PM7540 IC, lists the device features, and lists terms and acronyms used throughout this document. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | Defines the IC pin assignments.                                                                                                                                                                  |

| Chapter 3 | Defines the IC electrical performance specifications, including absolute maximum ratings and recommended operating conditions.                                                                   |

| Chapter 4 | Defines the IC mechanical specifications, including dimensions, thermal characteristics, moisture sensitivity, and markings.                                                                     |

| Chapter 5 | Presents procedures and specifications for mounting PM7540 ICs onto printed circuit boards (PCBs).                                                                                               |

| Chapter 6 | Discusses packing methods and materials for PM7540 shipments.                                                                                                                                    |

| Chapter 7 | Presents PM7540 IC reliability data including definition of the                                                                                                                                  |

## **1.2 Concise device description**

The PM7540 device (Figure 1-1) integrates all wireless handset power management, general housekeeping, and user interface support functions into a single mixed signal IC. Its versatile design is suitable for CDMA and non-CDMA handsets, and other wireless products such as PC PDAs.

The power management portion accepts power from common sources—battery, external charger, adapter, USB\_VBUS, coin cell backup—and generates all the regulated voltages needed to power the appropriate handset electronics. It monitors and controls the power sources, detecting which sources are applied, verifying that they are within acceptable operational limits, and coordinates battery and coin cell recharging while maintaining the handset electronics supply voltages.

On-chip voltage regulators generate 24 programmable output voltages using a combination of switched-mode power supplies and low-dropout voltage regulators, all derived from a common trimmed voltage reference. One regulator is dedicated for generating microphone bias voltages.

The device's general housekeeping functions include a 16-position analog multiplexer that has five internal connections, six hardwired external connections, and supports an additional 22 external connections. The internal connections are used to monitor on-chip functions such as the temperature sensor. The hardwired external connections access input power nodes such as VCHG, VBAT, etc. The 22 additional external connections are made using the IC's multipurpose pins that are configured as analog inputs and are routed through switch circuits to create five multiplexer inputs; these are available to monitor system parameters such as temperature and battery ID.

Chapter 7 Presents PM7540 IC reliability data, including definition of the qualification samples and a summary of qualification test results.

The multiplexer output signal's offset and gain is adjusted, then buffered and routed to the Mobile Station Modem<sup>TM</sup> (MSM<sup>TM</sup>) device for analog-to-digital conversion. Various oscillator, clock, and counter circuits are provided to initialize and maintain valid pulse waveforms and measure time intervals for higher-level handset functions. A dedicated controller manages the TCXO warm-up and signal buffering, and key parameters are monitored to protect against detrimental conditions.

Handset-level user interfaces are also supported. The IC includes four backlight or LED drivers with brightness (current) control that could be used for keypad, LCD, camera flash, and general-purpose drivers. A vibration motor driver alerts handset users of incoming calls, and a two-channel speaker driver with volume control can be used for audio alerts or speakerphone and melody-ringer applications. The speaker circuits accept stereo differential, stereo single-ended, and mono differential inputs, and can be configured for stereo or mono outputs. A video amplifier is included that allows the handset to be used as a camcorder or for slide presentations.

IC-level interfaces include the configurable serial bus interface (SBI) used by the MSM device to control and status the PM7540 IC. This bus is supplemented by an interrupt manager for time-critical information. Another dedicated IC interface circuit monitors multiple trigger events and controls the power-on/power-off sequences. A universal serial bus/on-the-go (USB-OTG) transceiver is included for interfacing the MSM device to computers as a USB peripheral, or connecting the MSM device to other peripherals. Removable user identity module (RUIM) level translators enable MSM device interfacing with external modules.

The PM7540 IC is a mixed signal BiCMOS device and is available in the 137-pin chip scale package (137 CSP) that includes several center ground pins for electrical ground and thermal relief.

Because the PM7540 IC includes so many diverse functions, its operation is more easily understood by considering major functional blocks individually. Therefore, this document (and all PM7540 documents within the set) is organized by the following device functionality:

- Input power management

- Output voltage regulation

- General housekeeping

- User interfaces

- IC interfaces

- Multipurpose pins (which can be configured to function within some of the other categories)

Most of the information contained in this device specification is organized accordingly, including the circuit groupings within the block diagram (Figure 1-1), pin descriptions (Chapter 2), and detailed electrical specifications (Chapter 3).

See *PM7540 Power Management IC User Guide* (80-VD691-3) for much more detailed descriptions of each PM7540 function and interface.

## **1.3 IC features**

- Complete power management, housekeeping, and user interface functions for wireless devices (CDMA, non-CDMA handsets, and PDAs)

- Input power management

- □ Valid external supply attachment and removal detection

- Supports unregulated (closed-loop) external charger supplies and USB supplies as input power sources

- □ Supports lithium-ion main batteries

- □ Trickle, constant current, constant voltage, and pulsed charging of the main battery

- □ Supports coin cell backup battery (including charging)

- Battery voltage detectors with programmable thresholds

- □ VDD collapse protection

- Charger current regulation and real-time monitoring for over-current protection

- □ Charger transistor protection by power limit control

- Control drivers for two external pass transistors and one external battery MOSFET (MOSFET is optional)

- □ Voltage, current, and power control loops

- □ Automated recovery from sudden momentary power loss

- Output voltage regulation

- One boost (step-up) switched-mode power supply (SMPS) for driving white LEDs and hosting USB-OTG

- Four buck (step-down), switched-mode power supplies for efficiently generating MSMC1, MSMC2, MSME, and PA supply voltages

- □ Supports dynamic voltage scaling (DVS) for MSMC1, MSMC2, and PA outputs

- 18 low-dropout regulator circuits with programmable output voltages, implemented using three different current ratings: 300 mA (four), 150 mA (ten), and 50 mA (four). These can be used to power MSMA, MSMP, MSME2, MMC, RFRX1, RFRX2, RFTX, TCXO, SYNT, RUIM1, RUIM2, USB, WLAN, MDDI, CAM, BT, AUX1, and AUX2 circuits.

- □ One MIC bias regulator circuit

- □ All regulators can be individually enabled/disabled for power savings

- □ Low power mode available on most regulators

- All regulated outputs are derived from a common bandgap reference (close tracking)

- Integrated handset-level housekeeping functions reduces external parts count, size, and cost

- □ Analog multiplexer selects from five internal and up to 28 external inputs

- Multiplexer output's offset and gain are adjusted, increasing the effective ADC resolution

- □ Adjusted multiplexer output is buffered and routed to an MSM device ADC

- Dual oscillators: a 32.768 kHz off-chip crystal and an on-chip RC assure MSM device sleep clock

- Crystal oscillator detector and automated switch-over upon lost oscillation

- □ Real-time clock for tracking time and generating associated alarms

- On-chip adjustments minimize crystal oscillator frequency errors

- □ Control TCXO warm-up and synchronize, deglitch, and buffer the TCXO signal

- **TCXO** buffer control for optimal QPH/catnap timing

- □ Multistage over temperature protection (smart thermal control)

- Integrated handset-level user interfaces

- □ Four programmable current sinks recommended as keypad backlight, LCD backlight, camera flash, and general-purpose drivers

- □ Vibration motor driver programmable from 1.2 to 3.1 V in 100 mV increments

- Two-channel speaker driver with programmable gain, turn-on time, and muting; configurable inputs and outputs capable of stereo or mono operation (drives external  $8-\Omega$  speakers with volume controlled 500 mW, each channel)

- □ Video (TV) amplifier allows use as a camcorder or for slide presentations

- IC-level interfaces

- □ Configurable SBI (three-wire or single-wire) for efficient initialization, status, and control

- □ Supports MSM interrupt processing with an internal interrupt manager

- Many functions monitored and reported through real-time and interrupt status signals

- Dedicated circuits for controlled power-on sequencing, including the MSM device's reset signal

- □ Several events continuously monitored for triggering poweron/poweroff sequences

- □ Supports and orchestrates soft resets

- USB-OTG transceiver for full-speed (12 Mb/s) and low-speed (1.5 Mb/s) interfacing of the MSM device to computers as a USB peripheral, or connecting the MSM device to other peripherals

- Two sets of RUIM level translators enable MSM device interfacing with external modules

- 22 multipurpose pins that can be configured as digital or analog I/Os, bidirectional I/Os, or current sinks; default functions support the two sets of RUIM level translators, power-on circuits, analog multiplexer inputs, an LED driver, and a selectable reference voltage output

- Highly integrated functionality in a small package 137-pin CSP with a several center ground pins for electrical ground, mechanical stability, and thermal relief

## **1.4 Terms and acronyms**

The following table defines terms and acronyms used throughout this document.

| Term or acronym | Definition                                     |

|-----------------|------------------------------------------------|

| ADC             | Analog-to-digital converter                    |

| API             | Application programming interface              |

| CDMA            | Code Division Multiple Access                  |

| CSP             | Chip scale package                             |

| EBI             | External bus interface                         |

| HAST            | Highly accelerated stress test                 |

| HIC             | Humidity indicator card                        |

| HTOL            | High-temperature operating life                |

| ID              | Identification                                 |

| Li 🔗            | Lithium                                        |

| MBB             | Moisture barrier bag                           |

| MPP             | Multipurpose pin                               |

| MSL             | Moisture sensitivity level                     |

| MSM             | Mobile Station Modem (trademarked by QUALCOMM) |

| MUX             | Multiplexer                                    |

| OTG             | On-the-go                                      |

| PA              | Power amplifier                                |

| РВМ             | Pulse burst modulation                         |

| РСВ             | Printed circuit board                          |

| PDA             | Personal digital assistant                     |

| PFM             | Pulse frequency modulation                     |

| PLL             | Phase-locked loop                              |

| РМ              | Power management                               |

| PWM             | Pulse width modulation                         |

| QCT             | QUALCOMM CDMA Technologies division            |

| RUIM            | Removable user identity module                 |

Table 1-2Terms and acronyms

| Term or acronym      | Definition                                                                                                                                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBI                  | Serial bus interface (3-wire unless designated as SSBI)                                                                                                                                                                                                                                              |

| SiGe                 | Silicon germanium                                                                                                                                                                                                                                                                                    |

| SMPS                 | Switched-mode power supply (DC-to-DC converter)                                                                                                                                                                                                                                                      |

| SMT                  | Surface mount technology                                                                                                                                                                                                                                                                             |

| SnPb                 | Tin/lead                                                                                                                                                                                                                                                                                             |

| SSBI                 | Single-wire serial bus interface                                                                                                                                                                                                                                                                     |

| support.cdmatech.com | QCT website address for technical assistance                                                                                                                                                                                                                                                         |

| ТСХО                 | Temperature-compensated crystal oscillator                                                                                                                                                                                                                                                           |

| USB                  | Universal serial bus                                                                                                                                                                                                                                                                                 |

| VCO                  | Voltage-controlled oscillator                                                                                                                                                                                                                                                                        |

| VCTCXO               | Voltage-controlled temperature-compensated crystal oscillator                                                                                                                                                                                                                                        |

| Zero-IF or ZIF       | Zero intermediate frequency; a radio architecture that converts received signals directly from RF to baseband, thereby eliminating the intermediate frequency necessary in super-heterodyne receivers. The transmit signals likewise eliminate the Tx IF, upconverting directly from baseband to RF. |

|                      |                                                                                                                                                                                                                                                                                                      |

#### Table 1-2 Terms and acronyms (continued)

# 2 Pin Definitions

The PM7540 IC is available in the 137-pin chip-scale package (137 CSP) that includes several center ground pins for electrical grounding, mechanical strength, and thermal continuity. Pin assignments are illustrated in Figure 2-1, listed in Table 2-1, and described in Table 2-2 through Table 2-9.

|   | 1              | 2             | 3             | 4                | 5                | 6                | 7                | 8              | 9             | 10              | 11             | 12            | 13             |   |

|---|----------------|---------------|---------------|------------------|------------------|------------------|------------------|----------------|---------------|-----------------|----------------|---------------|----------------|---|

| A | MPP_6          | VREG<br>_GP1  | VREG<br>_RFTX | SPKR_<br>OUT_R_P | SPKR_<br>OUT_R_M | SPKR_<br>OUT_L_M | SPKR_<br>OUT_L_P | VREG<br>_RFRX1 | VREG<br>_GP4  | VREG<br>_RFRX2  | VREG<br>_MSMA  | REF<br>_ISET  | REF<br>_GND    | А |

| в | VIDEO<br>_OUT  | VIDEO<br>_IN  | MPP_17        | SPKR_<br>IN_R_P  | SPKR_<br>IN_R_M  | SPKR_<br>IN_L_M  | SPKR_<br>IN_L_P  | VDD<br>_L_SPKR | VDD<br>_RF1   | VDD<br>_ANA     | VCOIN          | MPP_4         | VREG<br>_GP5   | в |

| с | ISNS_P         | ISNS_M        |               |                  | V                |                  | 20               | D. T           | 9             |                 |                | KPD_<br>PWR_N | REF<br>_BYP    | с |

| D | USB_<br>CTL_N  | CHG_<br>CTL_N |               | MPP_5            | MPP_18           | VDD<br>_RF2      | VDD<br>_R_SPKR   | MPP_3          | TCXO<br>_EN   | MSM<br>_INT_N   |                | VDD<br>_TCXO  | VREG<br>_TCXO  | D |

| E | KPD_<br>DRV_N  | VCHG          |               | BAT_<br>FET_N    | GND              | GND              | GND              | GND            | GND           | PS_<br>HOLD     |                | VREG<br>_SYNT | VREG<br>_GP6   | Е |

| F | LCD_<br>DRV_N  | VBAT          |               | MPP_19           | GND              | GND              | GND              | GND            | GND           | PON_<br>RESET_N |                | VDD<br>_GP6   | VDD<br>_MSME2  | F |

| G | VREG<br>_WLAN  | VDD<br>_WLAN  |               | MPP_20           | GND              | GND              | GND              | GND            | GND           | TCXO<br>_OUT    |                | MIC_<br>BIAS  | VREG<br>_MSME2 | G |

| н | FLSH_<br>DRV_N | USB<br>_ID    |               | USB_<br>OE_N     | GND              | GND              | GND              | GND            | GND           | SBCK            |                | TCXO<br>_IN   | VREG<br>_MSMP  | н |

| J | VREG<br>_5V    | MPP_21        |               | USB_<br>DAT      | GND              | GND              | GND              | GND            | GND           | SBST            |                | VDD<br>_MSMP  | VREG<br>_GP2   | J |

| к | VSW<br>_5V     | MPP_22        |               | USB_<br>SE0      | MPP_11           | MPP_12           | SLEEP<br>_CLK    | MPP_9          | MPP_10        | SBDT/<br>SSBI   |                | VDD<br>_GP2   | VREG<br>_MMC   | к |

| L | USB_<br>VBUS   | USB_<br>D_P   |               |                  |                  |                  |                  |                |               |                 |                | MPP_7         | V_<br>BACKUP   | L |

| м | VREG<br>_USB   | USB_<br>D_M   | MPP_13        | VREG<br>_PA      | MPP_16           | VREG<br>_MSMC2   | MPP_1            | VREG<br>_MSMC1 | VREG<br>_MSME | VDD<br>_RUIM    | MPP_8          | AMUX<br>_OUT  | XTAL<br>_IN    | м |

| N | MPP_14         | VIB_<br>DRV_N | MPP_15        | VSW<br>_PA       | MPP_2            | VSW<br>_MSMC2    | VDD<br>_C2_PA    | VSW<br>_MSMC1  | VDD<br>_C1_E  | VSW<br>_MSME    | VREG<br>_RUIM1 | VREG<br>_GP3  | XTAL<br>_OUT   | N |

|   | 1              | 2             | 3             | 4                | 5                | 6                | 7                | 8              | 9             | 10              | 11             | 12            | 13             |   |

|   |                | INPUT P       | WR MGT        |                  | GEN              | інк              |                  | IC             | l/F           |                 | Po             | wer           |                |   |

|   |                | OUTPU         | T V REG       |                  | USE              | R I/F            |                  | M              | PP            |                 | Gro            | und           |                |   |

Figure 2-1 PM7540 IC pin assignments (top view)

| Pin | Pin name <sup>2</sup> | Fcn <sup>3</sup> | Pin | Pin name          | fcn <sup>3</sup> | Pin | Pin name           | fcn <sup>3</sup> |

|-----|-----------------------|------------------|-----|-------------------|------------------|-----|--------------------|------------------|

| A1  | MPP_6 (RUIM_RST)      | MPP/ICI          | D8  | MPP_3 (CBL0PWR_N) | MPP/ICI          | G12 | MIC_BIAS           | OVR              |

| A2  | VREG_GP1 (CAM)        | OVR              | D9  | TCXO_EN           | GH               | G13 | VREG_MSME2         | OVR              |

| A3  | VREG_RFTX             | OVR              | D10 | MSM_INT_N         | ICI              | H1  | FLSH_DRV_N         | UI               |

| A4  | SPKR_OUT_R_P          | UI               | D12 | VDD_TCXO          | PWR              | H2  | USB_ID             | ICI              |

| A5  | SPKR_OUT_R_M          | UI               | D13 | VREG_TCXO         | OVR              | H4  | USB_OE_N           | ICI              |

| A6  | SPKR_OUT_L_M          | UI               | E1  | KPD_DRV_N         | UI               | H5  | GND                | GND              |

| A7  | SPKR_OUT_L_P          | UI               | E2  | VCHG              | IPM              | H6  | GND                | GND              |

| A8  | VREG_RFRX1            | OVR              | E4  | BAT_FET_N         | IPM              | H7  | GND                | GND              |

| A9  | VREG_GP4 (AUX1)       | OVR              | E5  | GND               | GND              | H8  | GND                | GND              |

| A10 | VREG_RFRX2            | OVR              | E6  | GND               | GND              | H9  | GND                | GND              |

| A11 | VREG_MSMA             | OVR              | E7  | GND               | GND              | H10 | SBCK               | ICI              |

| A12 | REF_ISET              | OVR              | E8  | GND               | GND              | H12 | TCXO_IN            | GH               |

| A13 | REF_GND               | OVR              | E9  | GND               | GND              | H13 | VREG_MSMP          | OVR              |

| B1  | VIDEO_OUT             | UI               | E10 | PS_HOLD           | ICI              | J1  | VREG_5V            | OVR              |

| B2  | VIDEO_IN              | UI               | E12 | VREG_SYNT         | OVR              | J2  | MPP_21             | MPP              |

| B3  | MPP_17                | MPP              | E13 | VREG_GP6 (BT)     | OVR              | J4  | USB_DAT            | ICI              |

| B4  | SPKR_IN_R_P           | UI               | F1  | LCD_DRV_N         | UI               | J5  | GND                | GND              |

| B5  | SPKR_IN_R_M           | UI               | F2  | VBAT              | IPM              | J6  | GND                | GND              |

| B6  | SPKR_IN_L_M           | UI               | F4  | MPP_19            | MPP              | J7  | GND                | GND              |

| B7  | SPKR_IN_L_P           | UI               | F5  | GND               | GND              | J8  | GND                | GND              |

| B8  | VDD_L_SPKR            | PWR              | F6  | GND               | GND              | J9  | GND                | GND              |

| B9  | VDD_RF1               | PWR              | F7  | GND               | GND              | J10 | SBST               | ICI              |

| B10 | VDD_ANA               | PWR              | F8  | GND               | GND              | J12 | VDD_MSMP           | PWR              |

| B11 | VCOIN                 | IPM              | F9  | GND               | GND              | J13 | VREG_GP2 (MDDI)    | OVR              |

| B12 | MPP_4 (CBL1PWR_N)     | MPP/ICI          | F10 | PON_RESET_N       | ICI              | K1  | VSW_5V             | OVR              |

| B13 | VREG_GP5 (AUX2)       | OVR              | F12 | VDD_GP6 (BT)      | PWR              | K2  | MPP_22             | MPP              |

| C1  | ISNS_P                | IPM              | F13 | VDD_MSME2         | PWR              | K4  | USB_SE0            | ICI              |

| C2  | ISNS_M                | IPM              | G1  | VREG_WLAN         | OVR              | K5  | MPP_11 (RUIM_M_IO) | MPP/ICI          |

| C12 | KPD_PWR_N             | ICI              | G2  | VDD_WLAN          | PWR              | K6  | MPP_12 (RUIM_IO)   | MPP/ICI          |

| C13 | REF_BYP               | OVR              | G4  | MPP_20            | MPP              | K7  | SLEEP_CLK          | GH               |

| D1  | USB_CTL_N             | IPM              | G5  | GND               | GND              | K8  | MPP_9 (RUIM_M_CLK) | MPP/ICI          |

| D2  | CHG_CTL_N             | IPM              | G6  | GND               | GND              | K9  | MPP_10 (RUIM_CLK)  | MPP/ICI          |

| D4  | MPP_5 (RUIM_M_RST)    | MPP/ICI          | G7  | GND               | GND              | K10 | SBDT/SSBI          | ICI              |

| D5  | MPP_18                | MPP              | G8  | GND               | GND              | K12 | VDD_GP2 (MDDI)     | PWR              |

| D6  | VDD_RF2               | PWR              | G9  | GND               | GND              | K13 | VREG_MMC           | OVR              |

| D7  | VDD_R_SPKR            | PWR              | G10 | TCXO_OUT          | GH               | L1  | USB_VBUS           | IPM              |

| Table 2-1 | PM7540 IC pin descriptions - listed in alpha-numeric order <sup>1</sup> |

|-----------|-------------------------------------------------------------------------|

|-----------|-------------------------------------------------------------------------|

| Pin | Pin name <sup>2</sup> | Fcn <sup>3</sup> |   | Pin | Pin name        | fcn <sup>3</sup> | Pin | Pin name         | fcn <sup>3</sup> |

|-----|-----------------------|------------------|---|-----|-----------------|------------------|-----|------------------|------------------|

| L2  | USB_D_P               | ICI              |   | M8  | VREG_MSMC1      | OVR              | N5  | MPP_2 (AMUX_IN2) | MPP/GH           |

| L12 | MPP_7 (GP1_DRV_N)     | MPP/UI           |   | M9  | VREG_MSME       | OVR              | N6  | VSW_MSMC2        | OVR              |

| L13 | V_BACKUP              | IPM              | ١ | M10 | VDD_RUIM        | PWR              | N7  | VDD_C2_PA        | PWR              |

| M1  | VREG_USB              | OVR              | I | M11 | MPP_8 (REF_OUT) | MPP/GH           | N8  | VSW_MSMC1        | OVR              |

| M2  | USB_D_M               | ICI              | ١ | M12 | AMUX_OUT        | GH               | N9  | VDD_C1_E         | PWR              |

| М3  | MPP_13                | MPP              | ١ | M13 | XTAL_IN         | GH               | N10 | VSW_MSME         | OVR              |

| M4  | VREG_PA               | OVR              |   | N1  | MPP_14          | MPP              | N11 | VREG_RUIM1       | OVR              |

| M5  | MPP_16                | MPP              |   | N2  | VIB_DRV_N       | UI               | N12 | VREG_GP3 (RUIM2) | OVR              |

| M6  | VREG_MSMC2            | OVR              |   | N3  | MPP_15          | MPP              | N13 | XTAL_OUT         | GH               |

| M7  | MPP_1 (AMUX_IN1)      | MPP/GH           |   | N4  | VSW_PA          | OVR              |     |                  |                  |

| Table 2-1 | PM7540 IC pin descriptions - listed in alpha-numeric order <sup>1</sup> | (continued) |

|-----------|-------------------------------------------------------------------------|-------------|

|-----------|-------------------------------------------------------------------------|-------------|

<sup>1</sup> More detailed descriptions of all I/Os are given below, organized according to the functional groups identified in note 3.

<sup>2</sup> All MPPs are configurable as explained in Section 3.4; the intended functions of MPP\_1 through MPP\_12 are included in their pin name column entries.

<sup>3</sup> Functional groups are:

.

| anonan groupe aren        |                           |                           |                        |  |

|---------------------------|---------------------------|---------------------------|------------------------|--|

| GH = general housekeeping | GND = ground              | ICI = IC-level interfaces | IPM = input power mgmt |  |

| MPP = multipurpose pin    | OVR = output V regulation | PWR = power supply        | UI = user interface    |  |

|                           |                           |                           |                        |  |

PM7540 pins are grouped according to their functionality (as defined in Table 2-1) and described below. Each functional grouping is presented in its own table:

| Table 2-2 | Input power management    |

|-----------|---------------------------|

| Table 2-3 | Output voltage regulation |

| Table 2-4 | General housekeeping      |

| Table 2-5 | User interfaces           |

| Table 2-6 | IC-level interfaces       |

| Table 2-7 | Multipurpose pins         |

| Table 2-8 | Power supply pins         |

| Table 2-9 | Ground pins               |

| Pin # | Pin name  | Pin type <sup>1</sup> | Functional description                                                                                                                                                                                                                                                                                         |

|-------|-----------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E2    | VCHG      | AI                    | A valid analog voltage at this pin is recognized by the PM7540 IC to be an external supply, and factors into the IC's power management operating mode. Connect an immediate 1.0 $\mu$ F capacitor to ground and a 10k resistor to ground.                                                                      |

| D2    | CHG_CTL_N | AO                    | Control signal for the external pass transistor – a low voltage turns on the pass transistor. This signal is pulled-up internally to $V_{CHG}$ or $V_{DD}$ depending upon the selected PM7540 operating mode.                                                                                                  |

| L1    | USB_VBUS  | AI, AO                | This pin is configured as an analog input or an analog output depending upon the type of peripheral device connected. Connect an immediate 2.2 $\mu$ F capacitor to ground and a 47k resistor to ground.                                                                                                       |

| D1    | USB_CTL_N | AO                    | Control signal for the external USB pass transistor - a low voltage turns on the pass transistor. This signal is pulled-up internally to the higher of two voltages, USB_VBUS or $V_{DD}$ .                                                                                                                    |