# Getting Started with MicroSim

Click on the icon for the topic you want to learn more about.

MicroSim's Family of Products

**Evaluation CD-ROM Limits**

**MicroSim Documentation**

What's New for Release 8.0

#### **How To Get Started**

Click on the icon for the topic you want to learn more about.

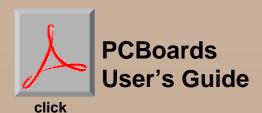

**Using MicroSim Schematics**

**Using MicroSim PSpice A/D**

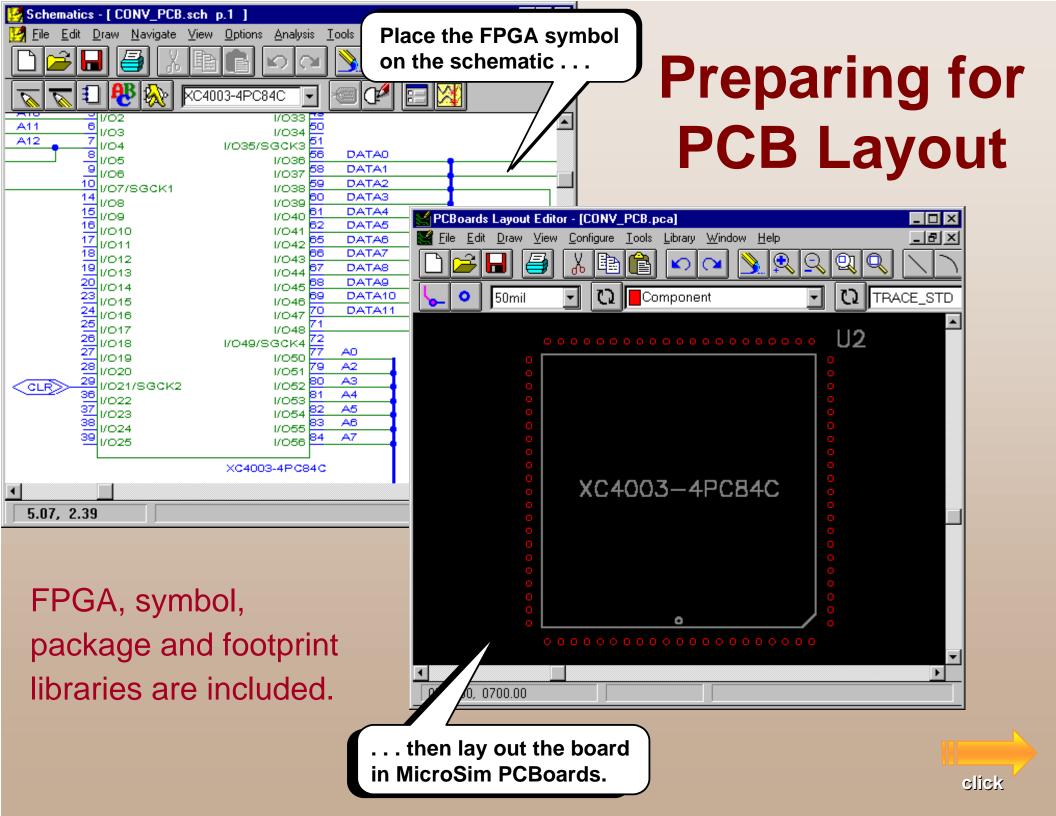

**Using MicroSim PCBoards**

**Using MicroSim PLSyn**

**Using MicroSim DesignLab**

Click on the icon for the topic you want to learn more about.

**Using MicroSim Schematics**

**Using MicroSim PSpice A/D**

**Using MicroSim PCBoards**

**Using MicroSim PLSyn**

**Using MicroSim FPGA**

## **Evaluation CD-ROM Limitations**

Click on the icon for the topic you want to learn more about.

**MicroSim Schematics**

MicroSim PSpice A/D

**MicroSim PCBoards**

#### **MicroSim Schematics Limitations**

- **▶** Schematic capture limited to one schematic page (A-size).

- → Maximum of 25 symbols can be placed on a schematic.

- Maximum of nine symbol libraries can be configured.

- Maximum of 20 symbols in a user-created symbol library.

- **▶** Sample library includes 22 analog and 140 digital parts.

#### MicroSim PSpice A/D Limitations

- **→** Circuit simulation limited to circuits with up to:

- ★ 64 nodes

- **★** 10 transistors

- **★ 2 operational amplifiers**

- **★** 65 digital primitive devices, or a combination thereof

- ★ 10 ideal transmission lines with not more than four non-ideal lines (lossy lines using RLGC parameters) and four coupled lines

- **▶** Device characterization limited to diodes.

- Stimulus generation limited to sine waves (analog) and clocks (digital).

#### **MicroSim PCBoards Limitations**

- ▶ Limited to 4 signal layers; 50 nets

- Limited to 30 components per layout

- **▶** Limited to 34 specific footprints:

| 199D/C/A1     | 199D/E/E | 2ck05   | ck06     | DIP4     |

|---------------|----------|---------|----------|----------|

| DIP6          | DIP8     | DIP14   | DIP16    | DIP18    |

| DIP24         | DO-35    | DO-41   | EDGE26   | JLCC84   |

| LCC84         | R2012    | R3216   | RC05     | RC07     |

| RC20          | SIP5     | SO14    | SO16     | TO-18    |

| TO-39         | TO-92    | TO-204A | TO-220AB | TO-247AB |

| DSHELL09-M-90 |          | HDR20   | Jump1    | Jump2    |

#### **MicroSim Documentation**

MicroSim documentation is available in both hardcopy and online formats.

- **★ MicroSim Schematics User's Guide**

- **★ MicroSim PSpice A/D & Basics+ User's Guide**

- **★ MicroSim PSpice & Basics User's Guide**

- ★ MicroSim PSpice A/D Reference Manual (this manual is online only)

- **★ MicroSim PSpice Optimizer User's Guide**

- **★ MicroSim PLSyn Programmable Logic Synthesis**

- **★ MicroSim PCBoards User's Guide**

- ★ MicroSim PCBoards Reference Manual (this manual is online only)

- **★ MicroSim PCBoards Autorouter User's Guide**

- ★ MicroSim Application Notes (this manual is online only)

- ★ Library List (this manual is online only)

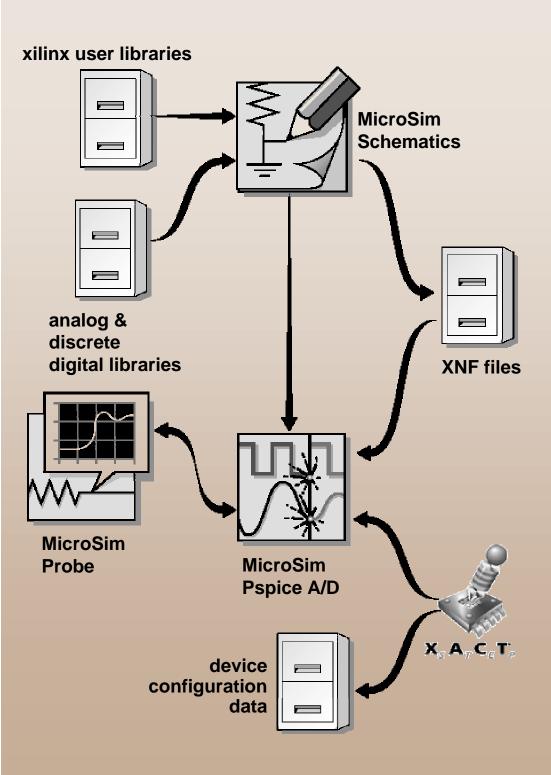

# What is MicroSim FPGA?

- Used to design Xilinx FPGAs (Field Programmable Gate Arrays).

- Part of MicroSim DesignLab and works with MicroSim Schematics for design entry, and MicroSim PSpice A/D for simulation.

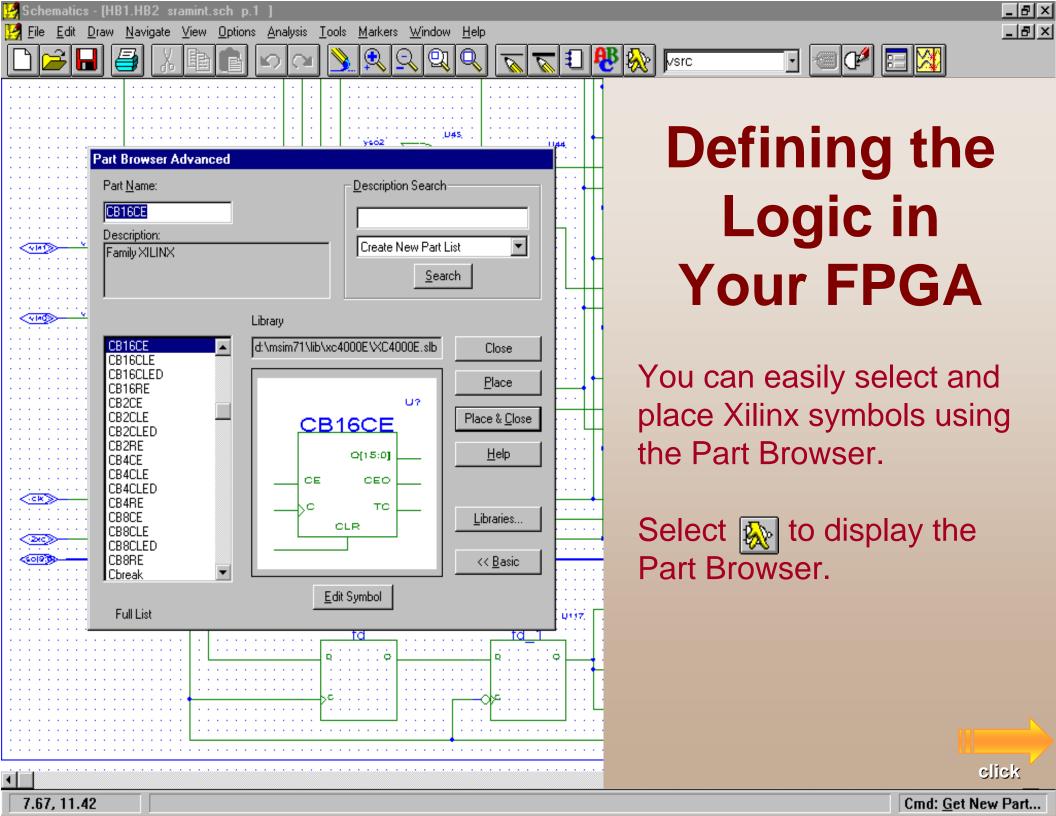

- ► Includes Xilinx Universal Library with symbols for XC2000, XC3000, XC4000, XC4000E, XC5200 device families, including XBLOX.

Only PC-based tool that can integrate FPGAs into your overall mixed analog/digital system design.

#### What is it Used For?

- ★ Creating integrated designs combining FPGAs with analog and discrete digital devices.

- **★ Designing** stand-alone FPGAs.

- ★ Performing functional simulation (before place and route).

- ★ Performing timing simulation (after place and route).

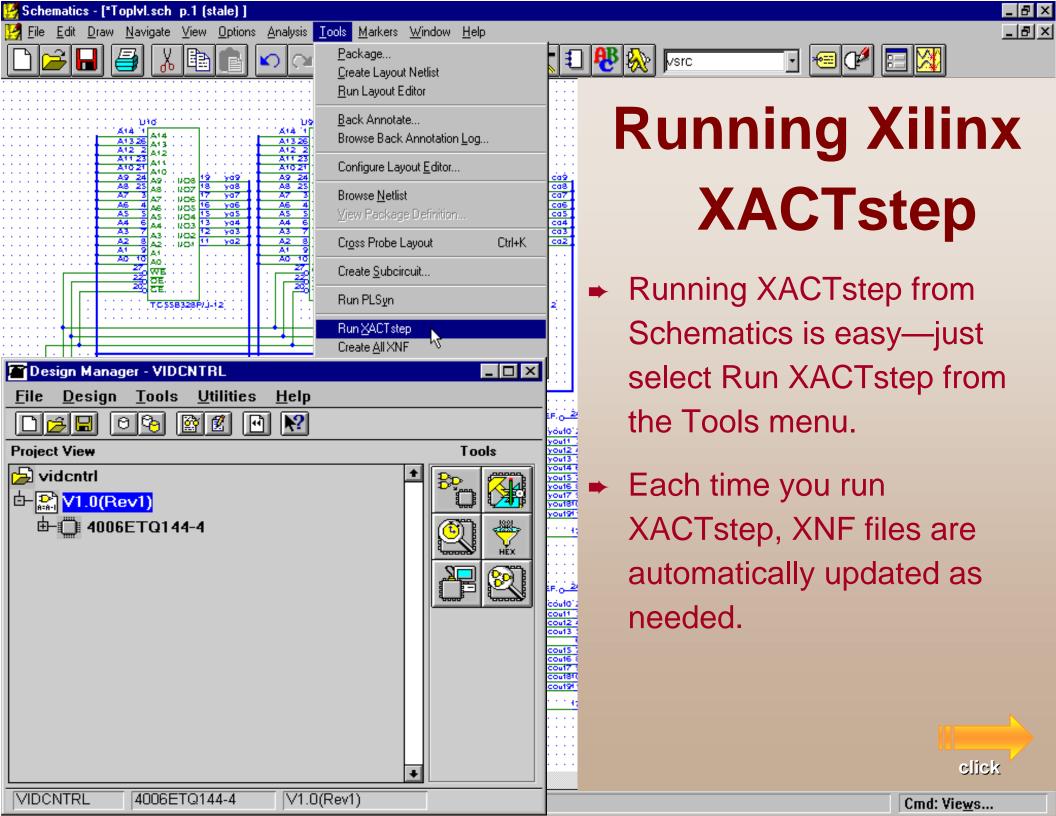

- ★ Accessing Xilinx XACTstep from MicroSim Schematics.

# Using MicroSim FPGA

- Design entry in MicroSim Schematics.

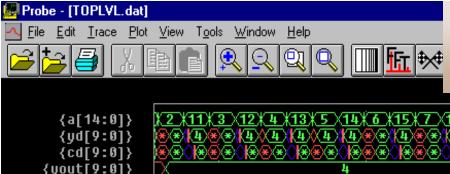

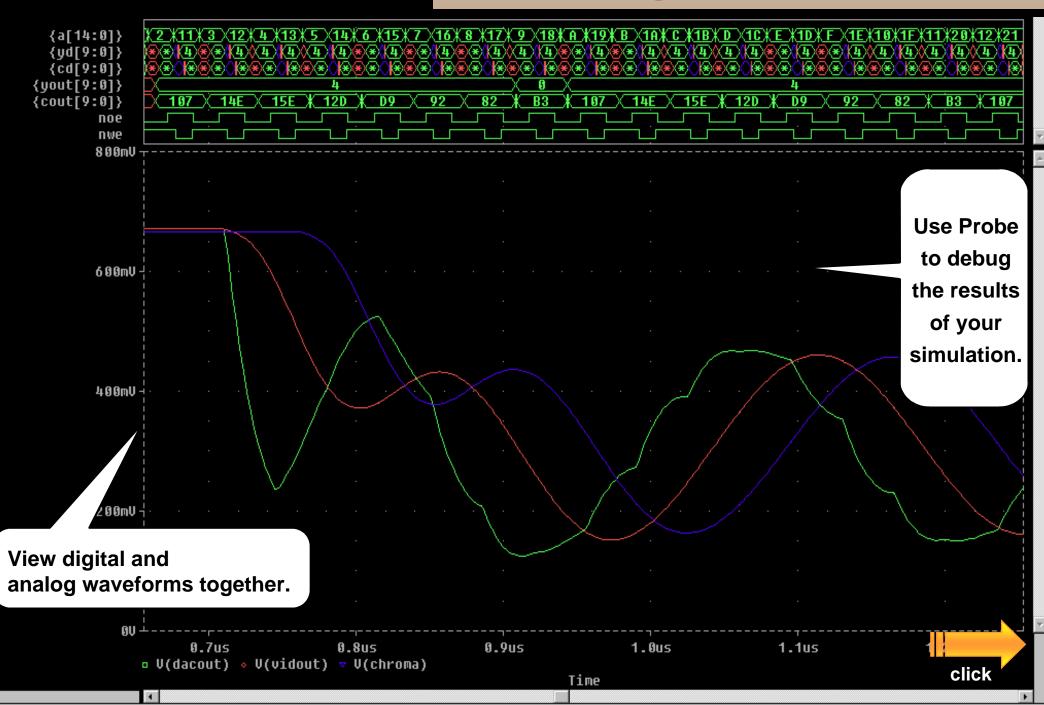

- Punctional simulation and analysis of simulation results in MicroSim Probe.

- O Placing and routing in Xilinx XACTstep.

- Timing simulation and analysis of simulation results in Probe.

# Functional Simulation

★ Use functional simulation to quickly debug designs prior to place and route.

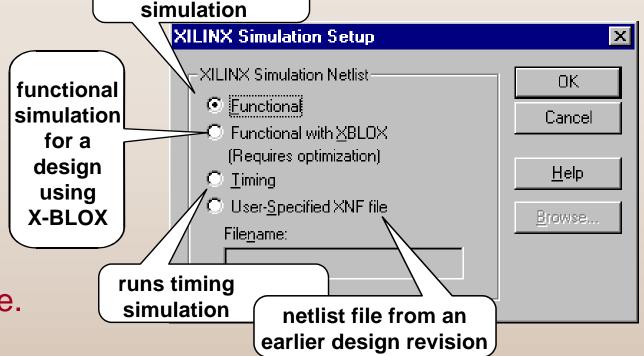

runs functional

- ★ For mixed designs, you can simulate the entire design or the FPGA only.

- ★ Easy simulation setup—select functional simulation in the Simulation Setup dialog box, then start simulation.

- ★ View simulation results in Probe.

# **Timing Simulation**

#### MicroSim FPGA

#### Bring accurate circuits to market faster!

- Only PC-based tool that integrates FPGAs with analog and discrete digital devices in a complete system design.

- Integrated simulation: access both functional and timing analysis through Schematics.

- Quick access to XACTstep.

# What is the MicroSim PSpice Optimizer?

The MicroSim PSpice Optimizer is a circuit optimization program that improves the performance of analog and mixed analog/digital circuits. With the PSpice Optimizer, you can:

- ★ Run optimizations

- **★** Explore performance tradeoffs

- ★ Fit model parameters

#### What is it Used For?

#### **Running optimizations**

The PSpice Optimizer performs iterative simulations, while adjusting the values of design parameters until performance goals, subject to specified constraints, are nearly or exactly met.

#### **Exploring performance tradeoffs**

The PSpice Optimizer provides graphical feedback showing performance. You can also tweak goal and constraint values to examine changes to parameter values.

#### Fitting model parameters

Given a parameterized model, a set of measured data points, and a good starting point for the parameter values, the PSpice Optimizer fits a more accurate model.

# Using the PSpice Optimizer

The PSpice Optimizer is fully integrated with other MicroSim programs. This means you can:

- **★ Design your circuit with MicroSim Schematics.**

- **★ Simulate with MicroSim PSpice A/D (or MicroSim PSpice).**

- **★ Analyze results with MicroSim Probe.**

- **★** Optimize performance within the same environment.

# **Using MicroSim PCBoards**

#### You can use MicroSim PCBoards to:

- ★ Specify printed circuit board structure as well as the components, metal and graphics required for fabrication.

- ★ Produce the artwork used in the manufacturing process, including information about the electrical and physical characteristics of the PCB layout.

## Starting MicroSim PCBoards

Start MicroSim PCBoards by doing one of the following:

In Schematics, from the Tools menu, select Run PCBoards.

From the Start menu, point to the MicroSim program group, then select the MicroSim PCBoards icon.

# Starting a New Layout

#### Start a layout using one of four methods:

- **★** Load a netlist (MicroSim Schematics or PADS-compatible) into a default layout.

- **★** Load a netlist (MicroSim Schematics or PADS-compatible) into a structured layout (template concept).

- **★** Modify an existing layout and rename it.

- **★** Place components and connections interactively (on-the-fly).

# Loading a Netlist

Netlist files contain a collection of component and connectivity declarations, and provide a convenient method for loading the layout.

- ★ MicroSim Schematic netlist (.nlf) describes the parts and connectivity as defined in the functional design created in Schematics.

- **★** PADS netlist (.pad) describes the parts and connectivity of a design in the PADS-compatible format generated by other schematic capture and layout programs.

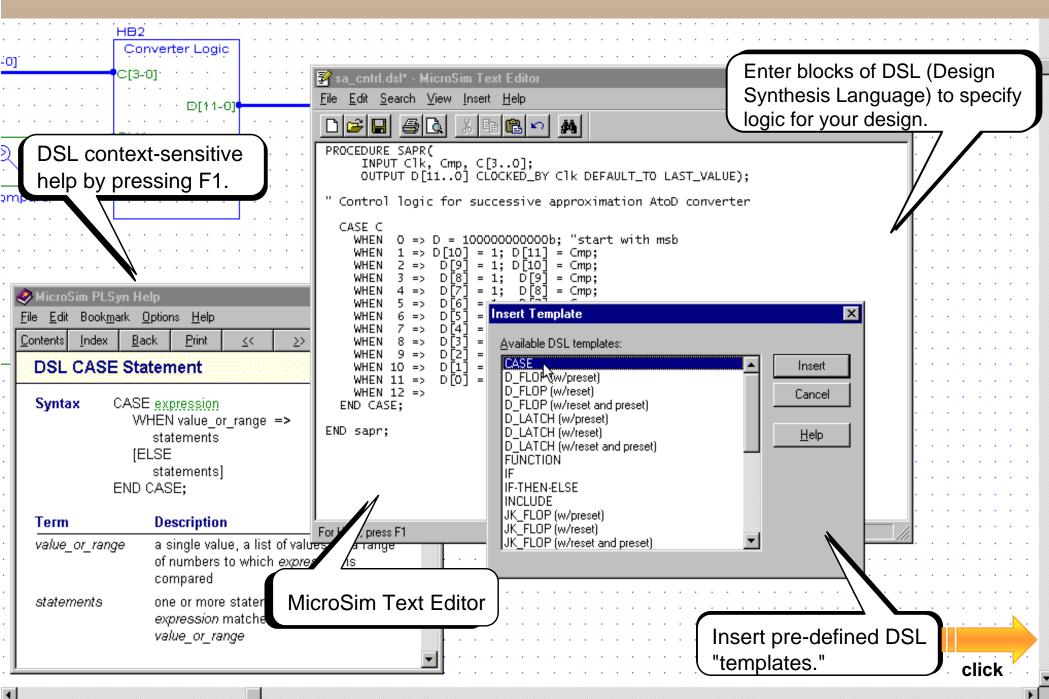

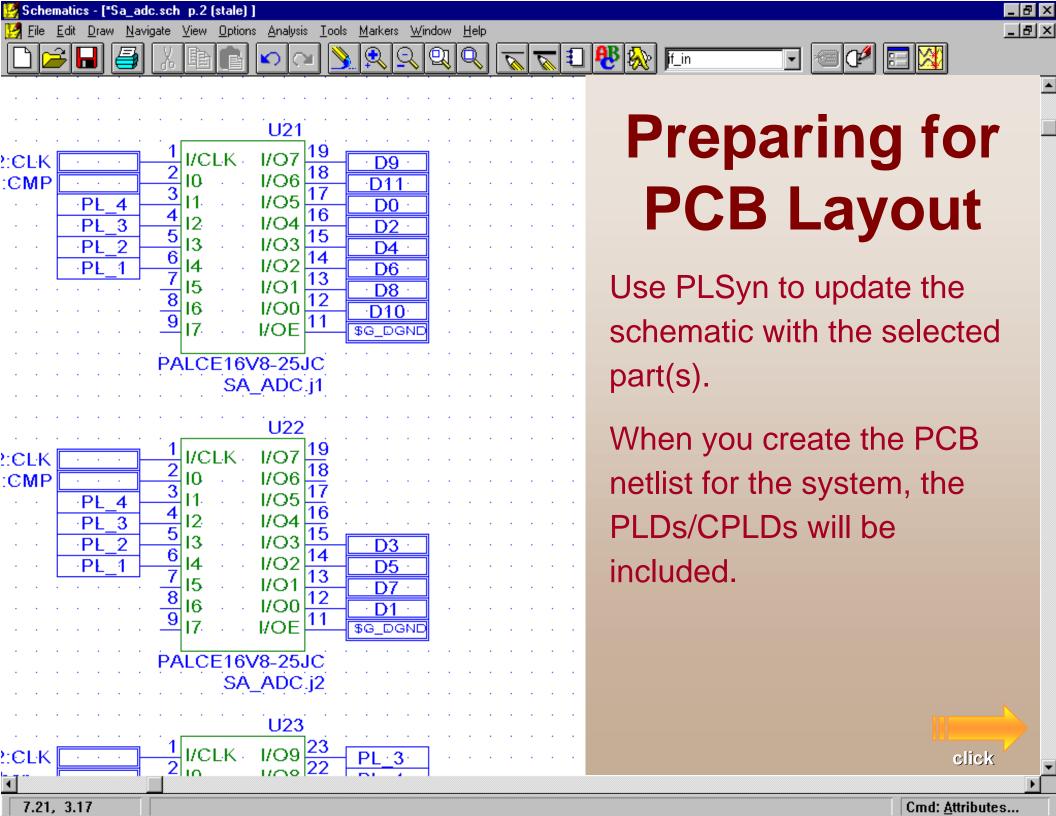

### What is MicroSim PLSyn?

- Used to design PLDs (Programmable Logic Devices) and CPLDs (Complex PLDs).

- Works with MicroSim Schematics and MicroSim PSpice A/D.

- ► Includes a part library with up to 3,500 PLDs and CPLDs from 12 manufacturers: Altera, AMD, Atmel, Cypress, ICT, Lattice, and more!

- Allows mixed-mode (schematic and language) design entry.

- Automatically partitions your design into multiple devices (with the PLSyn Partitioning option).

Only PC-based tool that can integrate PLDs and CPLDs into your overall mixed analog/digital system design.

#### What is it Used For?

- ★ Creating integrated designs combining PLDs and CPLDs with analog and discrete digital devices.

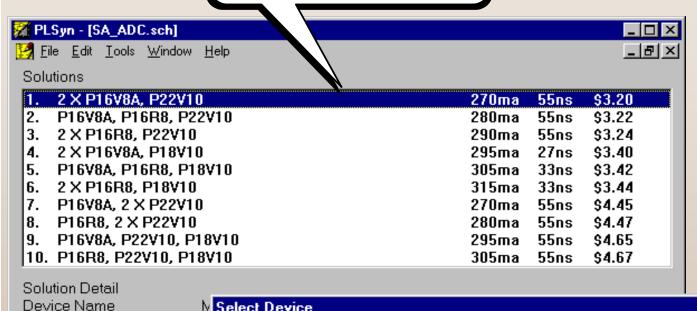

- ★ Generating a list of device solutions that meet your design specifications; you then select the configuration that best fits your design.

- ★ Performing functional simulation (before fitting and part selection).

- ★ Performing timing simulation (after part selection).

- **★ Generating** fuse map files.

#### Design Design **Phase** Simulate **Define** onstraints & **Priorities Implementation Phase** Fit/Partition Select **Device** Simulate with Timing **Program** Lay out **Device** the PCB

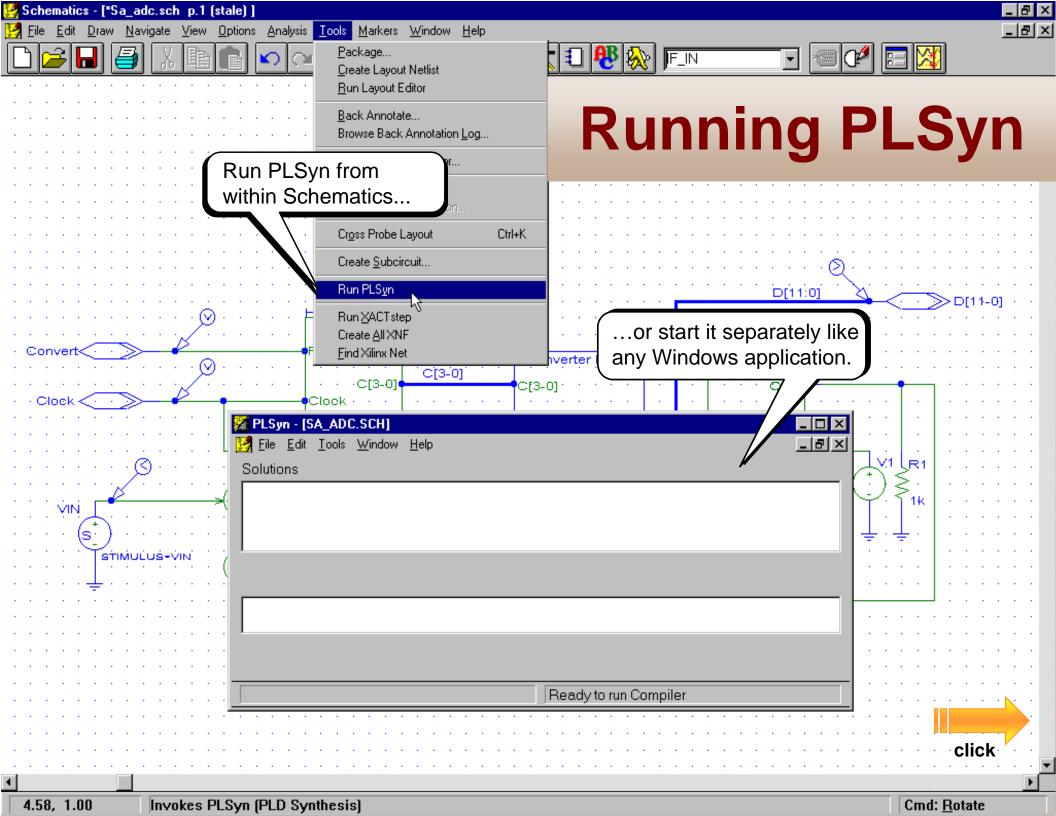

## Using MicroSim PLSyn

- Enter your design in Schematics.

- Perform functional simulation, and analyze simulation results in Probe.

- Set device constraints and priorities.

- 4 Run the PLSyn fitter to create a list of device solutions; solutions can be a single device or multiple devices (with the Partitioning option).

- Select a solution to implement your design.

- **6** Perform timing simulation, and analyze simulation results in Probe.

- Generate fuse maps to program the PLDs and/or CPLDs in your design.

# Placing DSL Blocks in Your Design

10.35, 1.72

Autosaving complete.

Cmd: Block

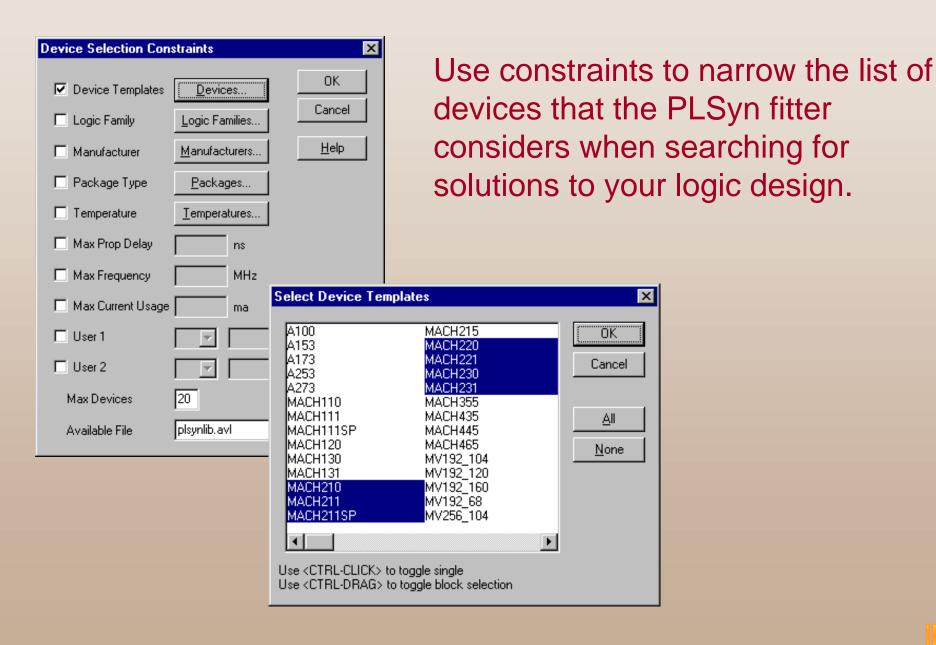

## **Setting Constraints**

Select the solution that best meets your requirements.

## Fitting the Logic

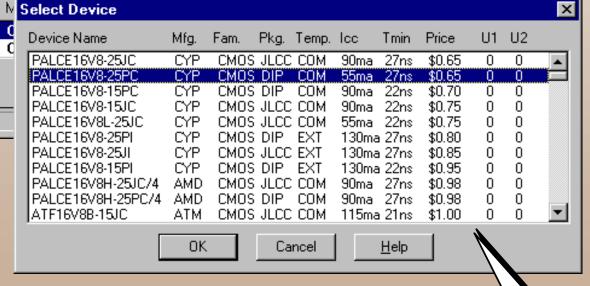

PALCE16V8-25JC

PALCE16V8-25JC

Run the PLSyn Fitter to find solutions based on your constraints. Solutions can be a single device or

multiple devices with the same or different architectures.

Select the part(s) to use for the chosen solution.

# **Functional & Timing Simulation**

## MicroSim PLSyn

#### Bring accurate circuits to market faster!

- Only PC-based tool that integrates PLDs and CPLDs with analog and discrete digital devices in a complete system design.

- Creates a list of device solutions to your logic design; you select the best solution.

- Integrated simulation: access both functional and timing analysis through Schematics.

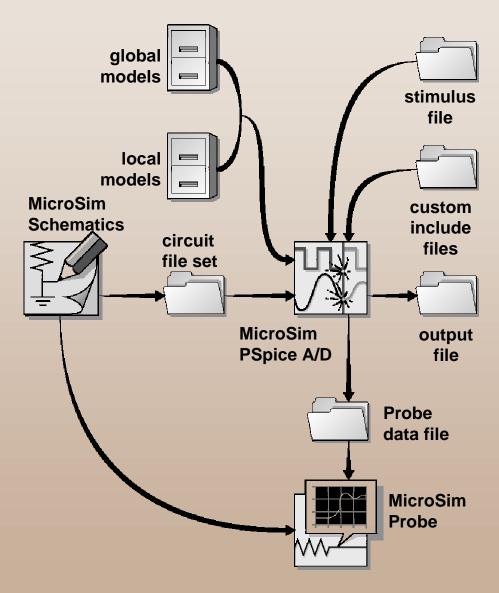

## **Using MicroSim PSpice A/D**

#### **The Simulation Process:**

- Create and prepare the schematic for simulation with MicroSim Schematics.

- Perform circuit simulation and analysis with PSpice.

- View simulation results with Probe.

# Simulating a Circuit with PSpice A/D

- → PSpice performs simulation and analysis by:

- Interpreting the information for the circuit in the Schematics files.

- 2 Automatically running the simulation.

- **3** Producing the Probe data file and simulation output file.

- ➤ When simulating, the wire connections to the pins of parts shown in a schematic are transformed into electrical node connections to device terminals that are interpreted by PSpice.

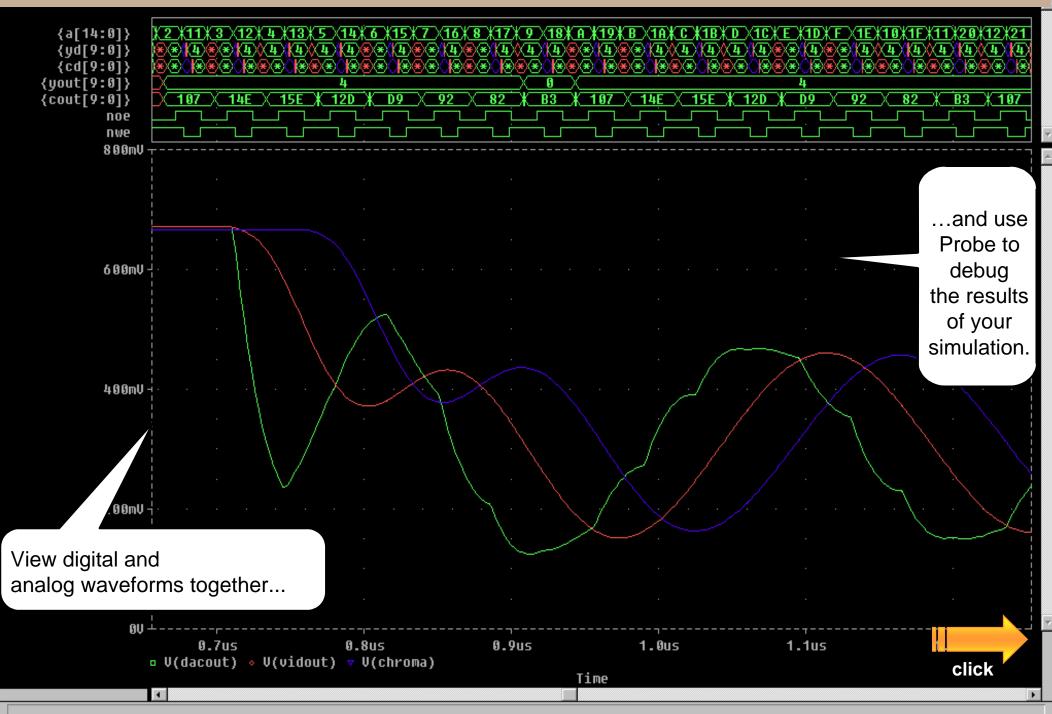

### **Displaying Simulation Results**

#### **Probe Data Files**

- ★ The Probe data file contains simulation results that can be viewed and manipulated in Probe, MicroSim's graphical waveform analyzer application.

- ★ Probe reads the data and displays waveforms reflecting circuit response at marked nets, pins, and devices in your schematic or for output variables that you can specify in Probe.

#### **Simulation Output Files**

**★** The simulation output file is an ASCII text file containing lists and tables describing the input circuit, the analysis directives, and the results of the specified simulations.

### Using MicroSim Schematics

Schematics is a front-end schematic capture program that you can use to:

create and edit designs

create and edit symbols

create and edit hierarchical designs

prepare a design for simulation

Schematics has extensive symbol libraries and a fully integrated symbol editor for creating your own symbols or modifying existing symbols.

## Starting a New Design

To start the schematic editor with an empty schematic page: from the Start menu, point to the MicroSim program group, then select Schematics.

If you already have Schematics running with another schematic displayed, click the New File button on the toolbar to start a new schematic.

## What's New in MicroSim Schematics

#### **Design Journal:**

- ★ Create a checkpoint of a design.

- **★** Select non-MicroSim files to save with design checkpoint.

- **★** Record notes with a checkpoint.

- **★** Restore a checkpoint.

- **★** Work on multiple design checkpoints simultaneously.

#### **Hierarchical Block Creation:**

- ★ Create a hierarchical block from an existing schematic.

- **★** Place pins automatically for each schematic port.

- **★** Accelerate bottom-up design and reduce errors that occur when manually placing pins.

## What's New in MicroSim Schematics

#### **Design Manager:**

- **★** Create and manage workspaces for better design organization.

- **★** Archive (and restore) designs.

- **★** Create a copy of a design.

- **★** Graphically browse to see a design's components and dependencies.

- **★** Drag-and-drop design components between designs.

- **★** Localize design dependencies. (Creates a self-contained instance of a design.)

- **★** Provide context-sensitive Help.

## What's New in MicroSim Schematics

#### **Annotation Graphics:**

- **★** Fill shapes for diodes, transistors, and other symbols.

- **★** Annotate the schematic with graphics as well as text.

- **★** Add notes to an area of the schematic.

- **★** Control graphic properties and text appearance.

- **★** Incorporate bitmap graphics, such as a company logo.

- **★** Create zoned borders.

- **★** Output DXF.

### WYSIWYG Orthogonal Rubberbanding:

- **★** Connectivity Watcher.

- **★** Automatic Stair Stepping.

- **★** Pin-to-Pin Connections are rubberbanded.

#### **Design Journal:**

- ★ Compare simulation results of different checkpoints (overlaid or in separate plots).

- ★ Display color-coded results in MicroSim Probe by design checkpoint.

- **★** See checkpoint and description properties of a trace in MicroSim Probe.

#### **Device Noise Spectra:**

★ View individual device noise contributions in MicroSim Probe. Data available include total noise contribution and the noise components of individual devices.

#### **Bias Point Display**

- ★ Displays the latest set of bias point information (Small Signal Bias/DC Bias point or initial transient analysis) within MicroSim Schematics. The information available for display includes analog voltages and digital states on wires, and currents into devices into device pins for both simulation primitives and macro-models.

- ★ Supports user-definable options (display ON/OFF, color, position, and precision control of displayed data, etc., which become the default for subsequent sessions).

- **★** Locates the source of topology errors such as floating nodes.

- ★ Displayed values can be printed (as shown on schematic) for documentation purposes.

#### **Symbols from Models**

- ★ Automatically generates symbols for the models extracted by MicroSim Parts.

- **★** Automatically generates the corresponding symbol libraries for simulation model libraries.

- ★ Automatically configures the newly created or updated symbol and model libraries for immediate use in MicroSim Schematics.

- **★** Bases the symbol generation on MicroSim's default symbol set or user-provided symbol set.

- **★** Generates symbols for analog, digital, or mixed-signal devices (both primitives and macro-models).

#### **BSIM3 V3 Built-In Model:**

**★** Support for the Berkeley BSIM3 V3 MOSFET model in MicroSim PSpice.

#### **Device Equations Option:**

- **★** Compiler manufacturer and version independence.

- **★** Device equations now in separately loaded DLL.

## What's New in MicroSim PCBoards

#### **Graphical Footprint Browser:**

- **★** Graphical part browser in layout editor.

- **★** Graphical footprint browser in footprint editor.

- **★** Checks for floating copper.

- **★** Generated Autorouting Rules Report.

#### **Interactive Netlist Read-In:**

- ★ Netlist read-in and problem resolution.

- ★ Complete netlist read-in on first try with problem reporting.

- **★** Interactive problem resolution to correct database.

#### **DXF Input and Output:**

**★** Imports and exports mechanical drawing files in DXF format.

## What's New in MicroSim DesignLab

- **★** Design Journal

- **★** Design Manager

- **★ WYSIWYG Orthogonal** Rubberbanding

- **★** Bias Point Display

- **★** Device Noise Spectra

- **★** Symbols from Models

- ★ BSIM3 V3 Built-In Model

- **★** Device Equations Option

- **★** Graphical Footprint Browser

- **★ Interactive Netlist Read-In**

- **★** DXF Input and Output

# What's New in MicroSim DesignLab

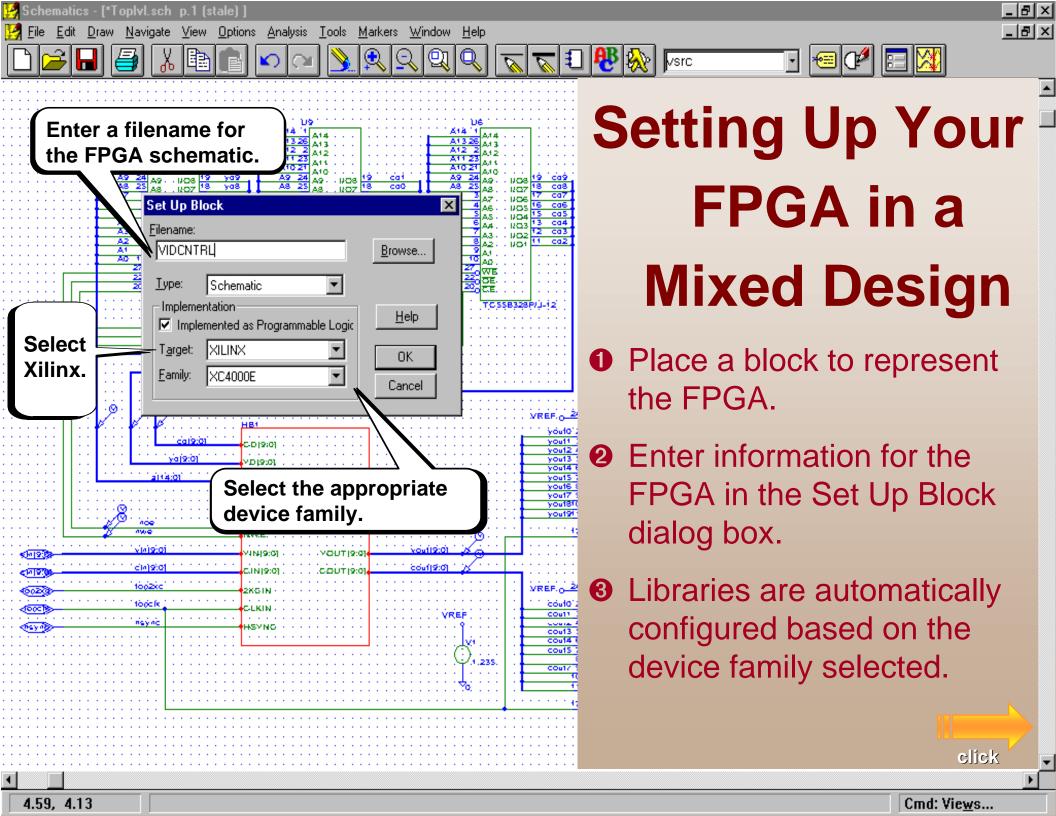

### Simulate Multiple Xilinx FPGAs

- ★ Each FPGA is simply represented as a hierarchical block and can be connected to analog and discrete digital components or other FPGAs.

- **★** Each FPGA can be from a different family.

- ★ Allows multiple-FPGA designs to be in different stages of completion.

#### **Import XNF**

- ★ Allows simulation of any Xilinx FPGA within a mixed analog/digital circuit.

- **★** Pins are added to the block automatically.

- ★ Supports XNF (Xilinx Netlist Format, versions 5 and 6) file from any source such as from obsolete design tools, synthesis tools, etc.

- **★** Automatically uses post place and route timing information if present in the XNF file.

click